Дифференциальный усилитель выходных сигналов запоминающего устройства

Иллюстрации

Показать всеРеферат

284027

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Кл. 21а<. 36/04

21ai, 37/88

Заявлено 14.Vill.1969 (№ 1357830/18-24) с присоединением заявки №

Приоритет

Опубликовано 14.Х.1970. Бюллетень ¹" 32

Дата опубликования описания 22.1.1971

МПК Н 03k 5/02

G 11с 7/02

УДК 681.327.12(088.8) Иомитет по делам изобретений и открытий при Совете Министров

СССР

Авторы изобретения

Ю. Г. Андреев, В. М. Головков, В. П. Салакатов и A. С

Заявитель

ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ ВЫХОДНЪ|Х СИГНАЛОВ

ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

Настоящее изобретение относится к импульсной технике и к области запоминающих устройств.

Известен дифференциальный усилитель выходных сигналов запоминающего устройства с п-секционной обмоткой считывания, содержащий транзисторы, источник тока, подключенный к эмиттерам транзисторов разных плеч дифференциального усилителя через резисторы обратной связи.

Недостатками известного усилителя являются большие затраты оборудования, значительно усложняющие его.

Описываемый усилитель отличается от известного тем, что он содержит и пар транзисторов, коллекторы которых подсоединены к двум общим для каждого из плеч дифференциального усилителя резисторам, а базы каждой пары транзисторов подключены к соответствующей обмотке считывания.

Указанное отличие позволяет существенно у п р ос тить усилитель.

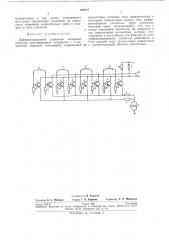

На чертеже показана принципиальная схема предлагаемого усилителя, содержащего, например, четыре пары транзисторов 1 — 4, которые образуют два плеча усилителя.

Эмиттеры всех восьми транзисторов объединены в две группы, подключенные к резисторам 5 и б, играющим роль отрицательной обратной связи. Резисторы 5 и б подключены к генератору тока 7. Соответствующим образом объединены в две группы и коллекторы транзисторов на резисторах 8 и 9. Секции обмотки считывания 10 — 18 (вторичные обмотки входных трансформаторов, соединенные с секциями) включаются между базами транзисторов каждой пары, к которым подключены также и согласующие резисторы 14 — 21.

Независимо от места возникновения сигнала на выходах 22 и 28 будет появляться усиленный сигнал.

Положительная особенность такого многовходово го дифференциального усилителя заключается в нелинейном суммировании поступающих одновременно по всем секциям сигналов помех. Так, например, помеха с четырех секций на выходе усилителя не более чем в два раза превышает аналогичную помеху от одной секции. Кроме того, много20 входовый усилитель допускает стробирование по входу путем подачи импульса стробирования на согласующие резисторы 14 — 21 выбранной секции. Длительность такого строба может составлять половину цикла, и появ25 ление помех во время действия его фронтов на выходе усилителя не является существенным.

Величина этой помехи незначительна, так как при подаче стробирующего импульса, по30 нижающего потенциал баз выбранной пары

284027

Предмет изобретения

22 гз

Составитель В, Рудаков

Техред Т. П. Курнлко Корректор Е. Н. Миронова

Редактор Б. С. Нанкнна

Заказ 3710711 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий прп Совете Министров СССР

Москва, W-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 транзисторов и тем самым запирающего остальные транзисторы усилителя, не происходит изменения коллекторных токов в каждом из плеч усилителя.

Дифференциалыный усилитель выходных сигналов запоминающего устройства с и-секционной обмоткой считывания, содержащий транзисторы, псточ?1ик тока, подключе?1ныи к эмиттерам транзисторов разных плеч дифференциального усилителя через резисторы обратной связи, отлича ощийся тем, что, с

5 целью упрощения усилителя, он содержит и пар тра нзисторов, коллекторы которых подсоединены к двум общим для каждого из плеч дифференциального усилителя резисторам, а базы каждой пары транзисторов подключены

10 к соответствующей обмотке считывания.