Запоминающий элемент

Иллюстрации

Показать всеРеферат

Сотое Советсккк

Соки листическив

Рбсоублди

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от а вт. свидетельства ¹â€”

Заявлено 05.Ч.1969 (№ 1327287/18-24) с присоединением заявки №вЂ”

Приор итет—

Опубликовано 14.Х.1970. Бюллетень ¹ 32

Дата опубликования описания 1 VI.1971

Ijë., 21a, 37/52

Комитет оо делам изобретений и открытий ори .Совете Министров

:СССР

МП1< 6 11с 11/38

УДК 681.327.67 (088.8) Автор изобретения

А. А. Алексеев

Горьковский исследовательский физико-технический институт

Заявитель

ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

Известен запоминающий элемент на тункельном диоде, резисторе и транзисторе, соединенный с числовой и разрядной шинами.

Недостатками известного за поминающего элемента является невысокая надежность, определяемая малым отношением тока записи к току помехи.

Описываемый запоминающий элемент отличается от известного тем, что .в нем к катоду туннельного диода подключен эмиттер транзистора, база которого соединена с числовой шиной, а коллектор подсоединен к разрядной шине.

Указанное отличие позволяет повысить надежность за поми нающето элемента.

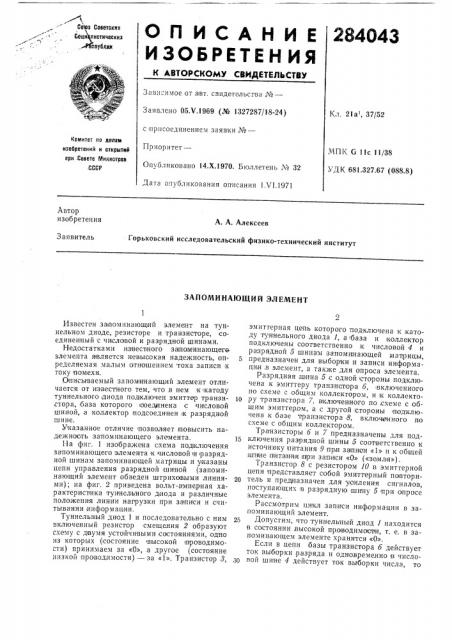

На фиг. 1 изображена схема подключения запоминающего элемента к числовой и разрядHoJi шинам запоминающей матрицы и у казаны цепи управления разрядной шиной (запоминающий элемент обведен штрихавьгми линиями); на фиг. 2 приведена вольт-амперная характеристика туннельного диода и различные положения линии нагрузки при записи и считывании информации.

Туннельный диод 1 и последовательно с ним включенный резистор смещения 2 образуют схему с двумя устойчивыми состояниями, одно из которых (состояние высокой проводимости) принимаем за «О», а другое (состояние низкой проводимости) — за «1». Транзистор 8, эмипттерная цепь которого подключена к .катоду туннельного диода 1, а база и коллектор подключены соответственно:к числовой 4 и разрядной 5 шинам запоминающей матрицы, 5 предназначен для выборки и записи информации,в элемент, а также для опроса элемента.

Разрядная шина 5 с одной стороны подключена к эмиттеру транзистора б, включенного по схеме с общим коллектором, и .к коллектоlр ру транзистора 7, включенного по,схеме с обшим эмиттером, а с другой, стороны подключена к базе транзистора 8, включенного по схеме с общим коллектором.

Транзисторы б и Т предназначены для под15 ключения разрядной шины 5 соответственно к источнику питания 9 при за пион «1» и к общей

;ши не п итания п ри записи «О» («земля»).

Транзистор 8 с резистором 10 в эмиттерной цепи представляет собой эмисгтерный повтори2р тель и предназначен для усиления сигналов, поступающих в разрядную шину 5 при опросе элемента.

Рассмотрим цикл записи информации в запоминающий элемент.

Допустим, что туннельный диод 1 находится в состоянии, высокой проводимости, т. е. в запоминающем элементе хранится «О».

Если в цепи базы транзистора б действует ток выборки, разряда и одновременно в числовой шине 4 действует ток выборки числа, то

284043 через транзистор 8 и туннельный диод 1 будет гротекать ток записи, так как переход базаэмиттер транзистора 8 открыт, а его коллектор подключен к источнику питания 9 через т р а из и стор б.

Под действием тока записи линия 11 нагрузки (см. фиг. 2) смещается и занимает положение 12.

И меть такой высокий уровень пока за писи, как указано на фнг. 2, с одной стороны, желательно, TBK как это гарантирует запись «1» в любой выбранный элемент, а с другой стороны, это недопустимо, потому что может произойти, пробой rreipesopa TlyIHIHeJlvHop диода 1.

Данная схема юбеспечивает выюю1иий у ровень така за(п иси и ogHoepeileHIHo и сключает возъюжию,сть пробоя тун нелыно го д ирда 1, так ка к TIpBHI3ието р, 3, закрьиваетюя, IKBIK толыко диюд 1 .переключится ia:ñIoIoòàÿIHHå ни зк1ой проводимост и.

EIcJIH од и н из двух тOIKoIB выбор к и о тсутетву ет,нап р имер, ток выбо рии числа), то через транзи(гтор 8, а следовательно, и черсз туннельный диод 1, ток,по меми n(ploITeKaть |не будет, та K как переход ба за-эмиттер транзн стора 8 закрыт, т. е..при выбю р ке юд ноияе нногo разряда другого числа ToIK помехи в да н ном запоминающем элемение праит ичс еки равен нулю.

При другом варианте возможного наличия помехи, когда TGK выборки разряда отсутствует, а ток выборки числа действует в число вой шине 4 1выбран другой разряд этого числа), то через переход база-эмиттер транзистора 8 и туннельный диод 1 будет протекать ток помехи, достаточный для записи ложной «1» в данный заиоминающий элемент.

Ли ния 11,нагрузки под действием тока помехи смещается до уровня 13. Для того, чтобы уменьшить ток помехи, а следовательно, предотвратить запись ложной «1», в цепь ба зы одновременно с током выборки числа;подается ток записи «О». При этом транзистор 7 под; ключает разрядную шину 5 к общей шине питания, в результате чего значительная часть входного тока тра,нзистора 8 через открытый переход база-коллектор утекает на общую шину питания, понижая тем самым уровень тока, помехи, протекающего через туннельный диод 1 и эмиттерную цепь транзистора 8.

В этом случае линия 11 нагрузки под действием тока помехи смещается до уровня 14.

5 Если туннельный диод 1 находится,в состоянии н изкой проводимости, т. е. элемент хранит «1», и если при этом в цепь базы транзистора 7 подается тюк записи «О», а в числовую шину 4 одновременно, подается ток выборки

10 числа, то произойдет запись «О», так как транзистор 8 .в данном случае работает,в ин версном включении. Линия 11 натрузки смещается до уровня 15 под действием тока записи «О», Рассмотрим цикл считывания информации.

15 Предлагаемая схема запоминающего элемента позволяет производить считывание информаци и без разрушения.

Для опроса элемента достаточно подать в числовую шину 4.ток опроса. При этом, если туннельный диод 1 находится в состоянии низкой проводимости, то в цепи базы транзистора

8 возникает ток, указывающий на наличие «1» в опрашиваемом элементе, так:как транзистор

8, как и при записи «О», работает в инверсном включении. При опросе элемента запись «О» исключена, так как .разрядная шина 5, подключенная к цепи базы эмиттерного повторителя, имеет большое сопротивление.

Если туннельный диод 1 находится .в соспоз0 янии высокой проводимости, то,в цепи базы транзистора 8 ток практически отсутствует, так KaIK ток опроса через открытый переход база-эмиттер транзистора 8 и туннельный диод 1 утекает на общую шину питания.

Амплитуда тока опроса определяется допустимой помехой в запоминающем элементе, туннельный диод 1 которого находится в состоянии высокой проводимости.

Предмет изобретения

Запоминающий элемент .на туннельном диоде, резисторе и транзисторе, соединенный с числовой и разрядной шинами, отлачающаася тем, что, .с целью повышения надежности за45 поминающего элемЕнта, к катоду туннельного диода подключен эмиттер транзистора, база которого соединена с числовой.шиной, а коллектор подсоединен к разрядной шине. 284048

Составитель В. Рудаков

Текред Т. П. Курилко

Корректор Л. Б. Бадылама

Редактор Б. С. Нанкина

Областная типография Костромского управления по печати

Заказ 7946 Тираж 480 Подписное

ЦИИИПИ Комитета по делам изобретений и открыпий при Совете Министров СССР, Москва, 5К-35, Раушская наб., д. 4/5