Реверсивный регистр сдвига

Иллюстрации

Показать всеРеферат

285054

Союз Советских

Соцнелистичесхил

Республик

Зависимое от авт, свидетельства ¹

Кл, 21ат, 36/22

21а, 37/64

Заявлено 04.Ч11.1969 (№ 1342808/18-24) с присоединением заявки №

Приоритет

Опубликовано 29.Х.1970. Бюллетень № 33

Дата опубликования описания 15.|.1971

Комитет по делам изобретений и открытий при Совете Министров

СССР

МПК G 11с 19!00

УДК 621.374.32 (088.8) Авторы изобретения

Е," ".Г-., М 4 . 1

В. А. Шубарев, П. И. Овсищер и И. М. Лазер

Заявитель

РЕВЕРСИВНЪ|Й РЕГИСТР СДВИГА

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении схем ЦВМ и цифровой автоматики.

Известен реверсивный сдвигающий регистр, выполненный на потенциальных элементах

«И — HE» («ИЛИ вЂ” HE»), каждый разряд которого состоит из запоминающей схемы, представленной триггером памяти и двумя коммутационными триггерами, и логической схемы, выполненной на двух элементах.

Для построения такого разряда необходимо восемь логических элементов. Время срабатывания разряда определяется суммой времен задержки запоминающей и логической схем.

Цель настоящего изобретения — повысить быстродействие сдвигового регистра при одновременном упрощении его схемы.

Это достигается путем включения в цепь триггеров памяти схемы запоминания дополнительного логического элемента «И вЂ” HE» («ИЛИ вЂ” НЕ»), играющего роль второго единичного плеча триггера, при этом триггеры па мяти осуществляют функции памяти и управления сдвигом вправо (влево).

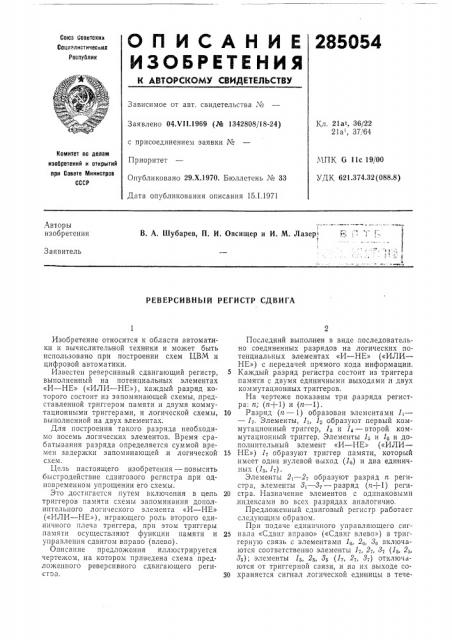

Описание предложения иллюстрируется чертежом, на котором приведена схема предложенного реверсивного сдвигающего регистпа, Последний выполнен в виде последовательно соединенных разрядов на логических потенциальных элементах «И — НЕ» («ИЛИ—

НЕ») с,передачей прямого кода информации.

5 Каждый разряд регистра состоит из триггера памяти с двумя единичными, выходами,и двух коммутационных триггеров.

На чертеже показаны три,разряда регистра: и; (n+1) и (n — 1).

10 Разряд (и — 1) образован элементами 1>— — 1т. Элементы, 1ь 1з образуют первый коммутационный триггер, 1з и 14 — второй коммутационный триггер. Элементы 1.- и 1е и дополнительный элемент «И — НЕ» («ИЛИ—

15 HE») 1-, образуют триггер памяти, который имеет один нулевой выход (16) и два единичных (1,, 1;).

Элементы 2 — 2-, образуют разряд и регистра, элементы 81 — 8т — разряд (n+-1) реги20 стра. Назначение элементов с одинаковыми индексами во всех разрядах аналогично.

Предложенный сдвиговый регистр работает следующим образом.

При подаче единичного управляющего сиг25 нала «Сдвиг вправо» («Сдвиг влево») в трпггерную связь с элементами 16, 2о, 8„включаются соответственно элементы 1-„2„8, (1;, 2;, 8;); элементы 1з-, 2е, 8е (1„2„8-,) отключаются от триггерной связи, и на их .выходе со30 храняется сигнал логической единицы в тече285054

&Фиг Ьмй

/л-г) разряд

Составитель Д, Голубович

Техред Л. Я, Левина Корректор T. А. Уманец

Редактор Ю. Полякова

Заказ 3860/3 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ние всего времени действия нулевого сигнала

«Сдвиг влево» («Сдвиг вправо»).

В момент действ ия тактового импульса информация, хранимая в разрядах регистра, сдвигается вправо (влево).

Быстродействие регистра определяется только временем срабатывания схемы запомина:ния.

Предмет изобретения

Реверсив|ный регистр сдвига с передачей информации в прямом ходе, разряд которого содержит два коммутационных триггера и триггер памяти, выполненные на логических потенциальных элементах «И — НЕ» («ИЛИ—

HE»), отличающийся тем, что, с целью упрощения схемы и повышения быстродействия, в каждый разряд введен дополнительно логический элемент «И — НЕ» («ИЛИ вЂ” НЕ»), соединенный триггерной связью с нулевым плечом триггера памяти; причем второй вход дополнительного элемента, подключен к единичному входу триггера памяти, а- третий вход— к шине «сдвиг влево»; выход дополнительного элемента соединен межразрядной связью со

10,входом первого коммутационного триггера предыдущего разряда, а единичный выход триггера памяти соединен межразрядной связью со входом первого коммутационного триггера, последующего разряда; дополни15 тельный, вход единичного плеча триггера памяти подключен к шине «сдвиг вправо».