Обучаемый классификатор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик,Зависимое от авт. свидетельства №

Заявлено 28.1V.1969 (№ 1326217118-24) с присоединением заявки №

Приоритет

Опубликовано 29.Х.1970. Бюллетень № 33

Дата опубликования описания 15.1.1971

Кл. 42m, 11/00

МПК G 061 11/00

УДК 681.325,65 (088.8) Комитет по делан изобретений и открытий при Совете Министров

СССР

Авторы изобретения

P И. Полонников, В. В. Александров и Ю. Г. Перевоз

Заявитель

ОБУЧАЕМЫЙ КЛАССИФИКАТОР

Обучаемый классификатор (ОК) относится к области конструирования адаптивных и диагностических устройств автоматики и технической кибернетики.

Известен обучаемый классификатор, содержащий матрицу адаптивных элементов, выполненных на трансфлюксорах, детектор максимума и схему индикации.

Двоичный обучаемый классификатор представляет линейное устройство, решающая функция которого R<(х) ) R (х), т =-,й l;

= 1,2...т, где т — число возможных решений. и

R, =;), ад. = Х бт. (1)

Здесь Х вЂ” опознаваемый двоичный п-мерный вектор, g,g — весовой коэффициент l-го класса

j ãî признака (j = 1,2...п).

ОК имеет два режима работы: режим обучения, в течение которого в каждой строке формируется вектор весовых коэффициентов

G,; режим классификации, когда предьявленный к опознаванию двоичный п-мерный вектор Х умножается на векторы весовых коэффициентов G = 1, 2...m.

Опознаваемый вектор Х относится к -му классу, если i-ая строка ОК имеет наибольшее суммарное значение выходного сигнала R;.

Целью изобретения является упрощение различения фазы выходных каналов и повыше»»е чувствительности устройства.

Для этого предлагаемый класспф катор =одержит в каждом канале схему,tìïóëüñíîãо смещения, а также m каналов из интегрирующих цепочек и усилителей постоянного сигнала с глубокой обратной связью.

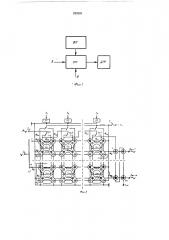

На фиг. 1 изображена блок-схема ОК; »а дп ф»г. 2 — принципиальная схема обучаемой матрицы; на фиг. 3 — электрическая схема детектора максимума.

ОК содержит обучаемую ма грпцу (ОМ); блок питания (БП), детектор максимума д5 (ДМ), где

Х вЂ” n — мерный двоичный код.

Y — указание при обучении.

ОМ содержит адаптивный элемент (АЗ), схе20 му смещения l — l„, и ключи, управляемые режимом работы ОК вЂ” Т, и П,.

Обучаемая матрица классификатора, имеющая размерность mXn, где m — число решений, принимаемых ОК, а п — число признаков, Q5 по которым принимается решение, выполнена на девяти отверстных трансфлюксорах.

Обмотки адаптивных элементов в столбцах и строках матрицы включены последоBàòåëь»о и образуют одновптковые шины. Обмотки

30 адаптации К„подмагнпч»вания К„и выход285353..-3 ные обмотки В, алементов образуют горизонтальные шины. Обмотки смещения W и считывания W, îáðàýóþò вертикальные шины, Цепь считывания образована последовательно включенными обмотками считывания W, столбцов матрицы и обмоткой в схемах импульсного смещения l,— l строк матрицы. В режиме обучения двоичный код (х,...х„1 поступает на реле P, — P„, контакты которых (К„1 — К„п) включены в цепях смещения W,„, столбцом матрицы трансфлюксоров. Ток смещения включается тумблером Т,. Одновременно переключатель П, выбирает одну из т строк обучаемой матрицы, в которой необходимо изменить весовые коэффициенгы д;, т. е. на строку подается ток адаптации 1,.

В режиме классификации (тумблер Т, выключен) в зависимости от значений х,...х„ (+ 1 илн — 1) на вход адаптивного элемента поступает ток считывания (j = 30 кгц) соответственно с фазой, равной 0 или 180 .

Последовательное включение выходных обмоток W, адаптивных элементов в строках

ОМ обеспечивает алгебраическое суммирование сигналов, считываемых с этих элементов, Суммарные импульсные сигналы в выходных обмотках строк обучаемой матрицы могут иметь различные фазы, что вызывает большие трудности при определении максимального сигнала. Схемы импульсного смещения l, — l no каждой из строк матрицы обеспечивают постоянство фаз суммарных сигналов, считываемых в выходные обмотки матрицы. Вольт-секундная площадь импульсных сигналов смещения должна быть не меньше максимально возможной вольт-секундной площади суммарных импульсных сигналов.

Детектор максимума (см. фиг. 3) имеет m идентичных каналов, связанных между собой отрицательной обратной связью. На входы детектора максимума с выходных обмоток строк обучаемой матрицы поступают двухполярные импульсы напряжения, считываемые с адаптивных элементов, содержащихся в строках обучаемой матрицы. С помощью диодов и интегрирующих RC-цепочек, включенных на входах каналов детектора максимума, производится детектирование и интегрирование импульсных сигналов и определяется IIx среднее значение. Каналы детектора максимума представляют собой трехкаскадные усилители напряжения. Первые и третьи каскады усилителей собраны на транзисторах типа p — n — p, а вторые каскады на n — р — n. Особенностью построения схемы детектора максимума является включение в цепи эмиттеров транзисторов общих сопротивлений, обеспечивающих отрицательную обратную связь между каналами детектора максимума на уровне каждого каскада усилителей напряжения, При поступлении на входы детектора мак=имума импульсных сигналов с выходов обучаемой матрицы

1р за счет отрицательных обратных связей между первыми двумя каскадами усилителей напряжения происходит обострение максимума в распределении средних значений импульсных сигналов, На уровне третьих каскадов

15 усилителей происходит выделение сигнала, имеющего максимальное среднее значение, вследствие чего загорается сигнальная лампочка в канале детектора максимума, а входе которого имеется максимальный сигнал.

2п Загорание сигнальной лампочки свидетельствует об отнесении предъявленного вектора Х к классу, соответствующему номеру данного ,канала. Разрешающая опособность детектора максимума составляет 10 — 12 л в в диапазоне0 — 4в.

Предмет изобретения

1. Обучаемый классификатор, состоящий из матрицы адаптивных элементов, детектора максимума и схемы индикации, отличающийся тем, что, с целью упрощения различения фазы выходных сигналов, в каждом из каналов по каждой строке матрицы адаптивных элементов, выполненных на девятиотверстных трансфлюксорах, содепжится схема импульсного смещения. выполненная на ферритовых кольцах с прямоугольной петлей гпстерезпса, 40 причем обмотки колец включены в общую цепь с выходными обмотками и обмотками считывания трансфлюксоров.

2. Обучаемый классификатор,по п. 1, огличающийся тем, что, с целью повышения

4 чувствительности, детектор максимума содержит т идентичных каналов,,каждый пз которых сосгавлен из последовательно соединенных интегрирующих RC-цепочек и трехкаскадного усилителя постоянного на,пряжения, выполненного на двух триодах типа р — и — р и одном ти IB п — р — п,,причем эмиттерная цепь триода каждото усилительного каскада включена на общий для т каналов резистор.

285353

Фиг 3

Составитель Ю. Розенталь

Редактор Н. С. Старостина Текред Т. П. Курилко Корректор В. И. Жолудева

Заказ 3878/6 Тираж 480 Подписпое

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4 5

Типография, пр. Сапунова, 2