Следящий интегратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОЬРЕтЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 03.11,1969 (И 1308254/18-24) с присоедннсш1см заявки №

Приоритет

Опубликовано 29.Х.1970. Бюллетень № 33

Дата опубликования описания 25.XI I.1970

Кл. 42итз, 15/32

42гпз, 7/18

Комитет по делам изобретений и открытий при Совете Министров

СССР

МПК, G 06f 15/32

G Обо 7/18

V+I(681,332.35(088.8) Лвторы изобретения

О. Б. Макаревич, В. П. Гондарев, Е. И. Духнич и Н. А, Пудзенков

Таганрогский радиотехнический институт

Заявитель

СЛ ЕДЯ Ш,и Й И НТЕ ГРАТОР

Предлагаемое изобретение относится к ооласти вычислительной техники, в частности, к структурам специализированных цифровых вычислительных машин, работающих с многоразрядными приращениями.

Известен следящий интегратор, состоящий из двух сумматоров, сдвигающего регистра, схемы анализа приращений, элемента памяти, блоков изменения знаков приращений, схем совпадения, инверторов, сборок.

При пользовании этими машинами в определенных случаях требуется большое количество логических блоков; известна также недостаточная гибкость цифровых интегрирующих машин с многоразрядными приращениями.

Предлагаемый следящий интегратор отличается тем, что выход источника потока приращений соединен со входом первого сумматора устройства, выход которого связан с первым входом второго сумматора, второй вход второго сумматора соединен со входом регистра и входом схемы анализа приращений, выходы которой через псрвую схему сборки подключены ко входу инвертора и к одному из входов первой схемы совпадения, другой вход первой схемы совпадения соединен с источником максимального поло?кительного приращения, выход инвертора и проме?куточный выход рсгистра связаны со входами второй схемы совпадения, выходы которой совместно с выходом первой схеМы совпадения через вторую схему сборки соединены с общим входом третьей и четвертой схем совпадения, второй вход третьей схемы совпадения подключен к

5 выходу схемы анализа приращений, вход первого блока изменения знака приращения через инвертор соединен со вторым входом третьей схемы совпадения, выход блока изменения знака приращений со местно с выходом

10 схемы соединения через третью схему соорки связаны со входами второго и третьего блоков изменения знаков приращений, выход второго соединен со входом элемента памяти, выход которого замкнут на вход первого сумматора, 15 управлгнощий вход третьего блока изменения знака приращений подключен к источнику сигналов управления, а его выход — к выходной шине интегратора.

Это позволяет увеличить гибкость цифровых

20 интегрирующих машин с многоразрядными приращениями и уменьшить количество решающих блоков.

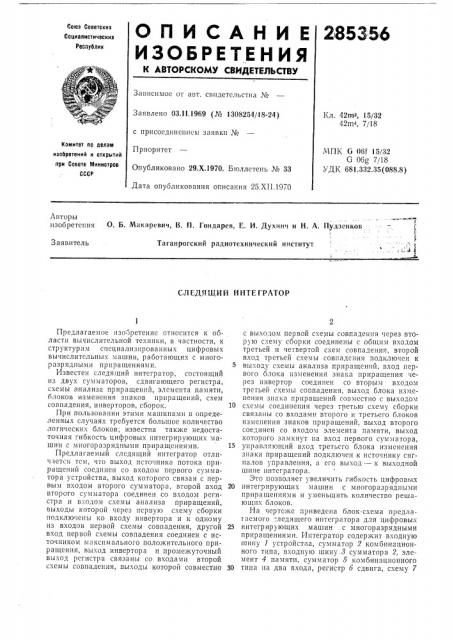

1-Iа чертеже приведена блок-схема предлагаемого -ледящего интегратора для цифровых

25 интегрирующих машин с многоразрядными приращениями. Интегратор содержит входную шину 1 устройства, сумматор 2 комбинационного типа, входную шину.з сумматора 2, элемент 4 памяти, сумматор 5 комбинационного

30 типа на два входа, регистр 6 сдвига, схему 7

285356

3 анализа приращений, выходную шину 8 сигнала максимального положительного приращения, выходную шину 9 сигнала минимального отрицательного приращения, собирательную схему 10 на два входа, схему 11 совпадения на два в«ода, вход 12 максимального положительного приращения, инвертор 18, схему 14 совпадения на два входа, выходную шину 15 регистра б, собирательную схему lб на два входа, схемы совпадения 17 и 18 на два вхо- 10 да, инвертор 19, собирательную схему 20 на два входа, блоки 21 — 22 изменения знака приращения, выходную шину 28 следящего интегратора, входную шину 24 управления блоком

22 изменения знака приращений, блок 25 из- 15 менения знака приращения.

Входной сумматор 2 предназначен для суммирования приращений, поступивших на в«одную шину 1, и приращений, поступающих на входную шину 8 по цепи обратной отрица- 20 тельной связи, состоящей из элемента 4 памяти и блока 21 изменения знака приращений.

Сумматор 5 предназначен для суммирования приращений с выхода сумматора 2 и содержимого регистра б. 25

Схема анализа приращений служит для выявления приращений, больших, чем максимальное положительное приращение, и меньших, чем минимальное отрицательное приращение. 30

Выходные шины 8 и 9 с«емы анализа приращений являются. управляющими шинами положительных и отрицательных максимальных приращений соответственно.

Собирательная схема 10 объединяет посту- 35 лающие с них сигналы.

Злемент 4 памяти запоминает на один шаг вычислений приращения с выхода собирательной схемы 20, превращая их тем самым в приращения предыдущего шага вычислений. 40

Регистр б сдвига служит для хранения начальной промежуточной информации. Кроме выхода соединенного со входом сумматора 5, регистр имеет выходную шину 15, через которую выдаются приращения, меньше по вели- 45 чине, чем абсолютная величина максимально используемых в устройстве приращений.

Инверторы 18 и 19 служат для получения на своем выходе инверсии сигнала, поданного 50 на er o вход.

Схема 14 совпадения предназначена для пропускания приращения с выходной шины 15 регистра б при отсутствии управляющего сигнала на выходе собирательной схемы 10. При 55 наличии сигнала на выходе схемы 10 схемы

14 совпадения закрыта сигналом с выхода инвертора 18.

Схема 11 совпадения пропускает максимальное положительное приращение, подавае- 60 мое на вход 12 от внешнего источника приращений при наличии разрешающего сигнала с выхода собирательной схемы 10.

Собирательная схема lб объединяет выходы схем 14 и 11 совпадения. 65

Схема совпадения (7, управляемая инвер. сией сигнала с выходной шины 9 схемы 7 анализа, предназначена для пропускания на вход собирательной схемы 20 приращений с выхода собирательной схемы lб, Схема совпадения 18, управляемая сигналом с выходной шины 9 с«емы 7, предназначена для пропускания приращений с выхода собирательной схемы lб на вход блока 25 изменения знака приращений.

Собирательная схема 20 объединяет выходы с«емы совпадения 17 и блока 25 изменения знака приращения. Выход схемы 20 соединен со входами блоков 21 и 22 изменения знака приращения.

Блок 21 предназначен для изменения знака выходного приращения, поступающего в цепь обратной связи.

Блок 22 используется для расширения технических и логических возможностей всего устройства. Знак приращения, поступающего на выходную шину 28 устройства, определяется сигналом управления, поданным на входную шину 24 блока 22 изменения знака прир а щения.

Следящий интегратор работает следующим образом.

От источника многоразрядных приращений на вход сумматора 2 поступает входная информация. На входную шину 8 того же сумматора подается приращение по цепи обратной отрицательной связи с выхода элемента 4 памяти. Результат суммирования поступает на один из входов сумматора 5, на другой вход которого подается содержимое накапливающего регистра б. Прн использовании данного следящего интегратора для преобразования полноразрядных чисел в поток многоразрядных приращений в регистр б записывается число, которое необходимо преобразовать в готок приращений. Полученная сумма с выхода сумматора 5 подается в регистр б и на вход схемы 7 анализа приращений. Сигнал на выходной шине 8 схемы 7 свидетельствует о том, что величина, поступившая с выхода сумматора 5, больше, чем возможное положительное приращение (+ AZxarcc) Сигнал на выходе 9 свидетельствует о том, что величина приращения меньше, чем минимальное отрицательное приращение (— Л Z„,„„). Сигнал с выходной шины 8 или 9, проходя через собирательную схему 10, поступает на один вход схемы 11 совпадения, а на ее другой вход 12 из устройства управления подается максимальное положительное приращение (+ AZ„a„,).

Одновременно сигнал с выхода сборки 10, проходя через инвертор 18, запрещает прохождение через схему 14 совпадения всякой информации с выходной шины 15 регистра б.

Следовательно, информация, соответствующая максимальному положительному приращению, поступает на схему lб и на схемы совпадения 17 и 18. Если схема 7 фиксировала сигнал на шину 8, то схема совпадения 17 бу285356 дет открыта через инвертор 19 и приращение, пройдя собирательную схему 20, поступит через блок 21 изменения знака в цепь обратной связи.

Блок 21 инвертирует выходное приращение перед запоминанием его на элементе 4 памяти. С выхода же собирательной схемы 20 приращение поступает на блок 22, где его величина ЛЛ,„и„уменьшается на + 1 или — 1 в зависимости от управляющего сигнала на входной шине 24 блока 22. Затем приращение поступает на выходной шине 28 устройства.

Если схема 7 фиксировала сигнал на выходной шине 9, то приращение с выхода собирательной схемы 1б через схему совпадения инвертирует свой знак на блоке 25 изменения знака приращения. В дальнейшем ход информации тот же, что и в первом случае.

В тех случаях, когда нет сигнала ни на одном из выходных шин 8, 9 схемы 7 анализа, это означает, что в регистре находится приращение по величине меньше максимального положительного и больше минимального отрицательного приращения, и оно должно без «аких-либо преобразований попасть на выход устройства. С этой целью в регистре б имеется дополнительная выходная шина 15, передача информации через которую осуществляется с задержкой на время анализа информации в схеме 7. Информация с выходной шины 15 регистра б через схему 14 совпадения, собирательную схему 1б, схему 17 совпадения и собирательную схему 20 появляется на выходной шине 28 устройства.

Предмет изобретения

Следящий интегратор, состоящий из двух сумматоров, сдвигающего регистра, схемы анализа приращений, элемента памяти, блоков изменения знаков приращений, схем совпадения, инверторов, сборок, отличающийся тем, что, с целью сокращения числа решающих блоков, увеличения логических возможностей цифровой интегрирующей машины с многоразрядными приращениями, выход источника потока приращений соединен со входом первого сумматора устройства, выход которо10 го связан с первым входом второго сумматора, второй вход второго сумматора соединен со входом регистра и входом схемы анализа приращений, выходы которой через первую схему сборки подключены ко входу инвертора, 15 и с одним из входов схемы совпадения, другой вход первой схемы совпадения соединен с источником максимального положительного приращения, выход инвертора и промежуточный выход регистра связаны со входами второй

20 схемы совпадения, выходы которой совместно с выходом первой схемы совпадения через вторую схему сборки соединены с общим входом третьей и четвертой схем совпадения, второй ьход третьей схемы совпадения подключен к

25 выходу схемы анализа приращений, вход первого блока изменения знака приращения через инвертор соединен со вторым входом третьей схемы совпадения, выход блока изменения знака приращений совместно с выходом

30 схемы соединения через третью схему сборки связаны со входами второго и третьего блоков изменения знаков приращений, выход второго соединен со входом элемента памяти, выход которого замкнут на вход первого сум35 матора, управляющий вход третьего блока изменения знака приращений подключен к uc Iî÷íèêó сигналов управления, а его выход— к выходной шине интегратора.

285356

Составитель А. Плащин

Редактор Ю. Д. Полякова Техред А. А. Камышникова Корректор Л. Л. Евдонов

Заказ 3673/l4 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4/5

Типогр;п11ия, Ilp. Сапунова, 2