Всесоюзная )я*иятйо-техш!':г кдг!библио-tka 1

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 290452

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 12.VIII.1969 (PPo 1356112/18-24) МПК Н 03k 19/10 с присоединением заявки №

Приоритет

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 681.332.65 (088.8) Опубликовано 22.XII.1970. Бюллетень № 2 за 1971

Дата опубликования описания 16.III.1971

Лвтор изобретения

В. М. Железняков

Физико-технический институт имени А. Ф. Иоффе

Заявитель

ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

<к,,=Згб, Очевидно, что! тл тэ, -- тэ, — !б,(-, ° I) 20 !! — "э тх. р-и-р тд и-р-и

Предлагаемое изобретение относится к вычислительной технике и может быть использовано в вычислительных и управляющих системах повышенного быстродействия, ядерной электронике и в технике измерений наносекундных процессов.

Известны логические элементы, содержащие р — и — p транзистор, эмиттер которого соеди-! нен с катодом туннельного диода (7Д).

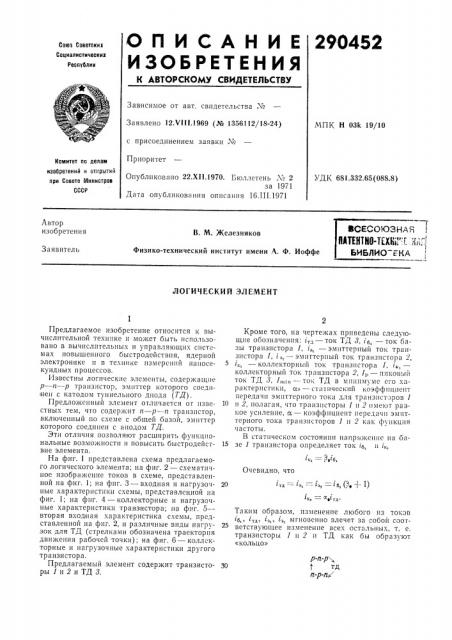

Предложенный элемент отличается от известных тем, что содержит и — р — и транзистор, включенный по схеме с общей базой, эмиттер которого соединен с анодом ТД.

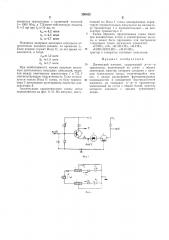

Эти отличия позволяют расширить функциональные возможности и повысить быстродействие элемента, На фиг. 1 представлена схема предлагаемого логического элемента; на фиг. 2 — схематичное изображение токов в схеме, представленной на фиг. 1; на фиг. 3 — входная и нагрузочные характеристики схемы, представленной на фиг. I; на фпг. 4 — коллекторные и нагрузочные характеристики транзистора; на фиг. 5— вторая входная характеристика схемы, представленной на фиг. 2, и различные виды нагрузок для ТД (стрелками обозначена траектория движения рабочей точки); на фиг. 6 — коллекторные и нагрузочные характеристики другого транзистора.

Предлагаемый элемент содержит транзисторы1и2иТДЗ.

Кроме того, на чертежах приведены следующие обозначения: i„— ток ТД 3, 1б, — ток базы транзистора 1, 4, — эмнттерный ток транзистора 1, 1,! — эмнгтерный ток транзистора 2, — коллекторный ток транзистора 1, i„.„— коллекторный ток транзистора 2, I» — пиковый ток ТД 3, 1„„„— ток ТД в минимуме его характеристики, аб — статический коэффициент передачи эмнттерного тока для транзисторов 1

10 и 2, полагая, что транзисторы 1 н 2 имеют равное усиление, а — коэффициент передачи эмнттерного тока транзисторов 1 н 2 как функция частоты.

В статическом состоянии напряжение на ба15 зе 1 транзистора определяет ток 4, и i„., Таким образом, изменение любого из токов

Eg,, 1„, т„, т,, мгновенно влечет за собой сооТветствующее изменение всех остальных, т. е. транзисторы 1 и 2 и ТД как бы образуют

«КОЛЬЦО»

290452

Поэтому управление схемой может осуществляться изменением любого из этих токов.

На фиг. 3 изображена входная вольт-амперная характеристики (кривая а) схемы со стороны базы транзистора 1, т. е. для Вход 1.

Здесь же показаны различные виды нагрузок, осуществляемые в схеме (кривые б, 0, г и д).

Такой вид входной характеристики и нагрузочных линий есть результат включения ТД именно между эмиттерами транзисторов 1 и 2 с разными типами проводимостей.

Нагрузкой ТД по постоянному току со стороны транзистора 1 является сам транзистор 1, и поэтому кривой б на фиг. 3 будет соответствовать кривая б ча фиг. 4, сжатая в 1 — 2 раза по току.

Такой масштаб тока на фиг. 3 отображает усилительные свойства транзистора 1.

Представленное на фиг. 4 семейство коллекторных характеристик транзистора 1 есть ряд эквидистантных линий. Очевидно, что загрузочные линии на входной характеристике также будут эквидистантными, и чтооы осуществить в схеме режим с двумя устойчивыми состояниями необходимо иметь:

R 1г(— ) vl где (r (— ) „, ) — среднее значение модуля отрицательного сопротивления туннельного диода 3; % — сопротивление резистора 4.

B том случае, когда входом схемы служит вход II, входная характеристика будет иметь вид, показанный на фиг. 5, и существенно отличаться лишь масштабом по токовой оси.

Таким образом, из фиг. 3, 5 следует, что в схеме могут быть осуществлены следующие режимы: режим с одним устойчивым состоянием (кривые б и д на фиг. 3 и 5); режим с двумя устойчивыми состояниями (кривые в на фнг.

3 и 5); автоколеоательный режим (кривая г

va фиг. 3 и 5).

Кроме того, представляется возможным осуществление усилительного режима в схеме, когда линия нагрузки совпадает на некотором участке с линией отрицательного сопротивления на входной характеристике. Этот режим схемы не исследовался.

Из вышеизложенного следует, что в зависимости от величины сопротивлений резисторов

4 и 5 схема может работать как: одновпбратор от входных импульсов отрицательной полярности; одновибратор от входных импульсов положительной полярности; элемент с двумя устойчивыми состояниями, т. е. триггер и автогенератор разрывных колебаний.

Следует отметить, что полярность рабочих импульсов для схемы можно изменить, поменяв местами транзистор 1 и транзистор 2 и соответственно изменив полярность включения

ТД и источников питания Е и Е. При этом, если E =E и резисторы б и 7 равны, схема останется в том же режиме, изменив только полярность рабочих и выходных импульсов на об р атную.

Рассмотрим теперь динамику схемы при работе ее как одновибратора от входных импульсов отрицательной полярности. В этом случае на фиг. 3 ему соответствует нагрузочная линия (кривая б) при Ri,=Î, При поступлении а

Вход 1 схемы импульса напряхкения ток базы 4, транзистора 1 начнет увеличиваться (начнут увеличиваться и токи /,, г,,: 1„-, =,,, t„. ).Спустя время 1=1-,, которое обусловлено процессами диффузии носителей в базе транзистора 1 i,-, достигнет значения 1„. ТД через (1З вЂ” время заряда собственной емкости

ТД) переключится за время t =t.„â состояние с высоким напряжением на нем.

До этого момента токи в схеме выражались

15 следующими соотношениями:

i ý, —,, — тл — iq1(!+ 1)

i,, =1б, к,,: б,(+ 1)

С момента перека.очения ТД транзисторы будут управляться со стороны эмиттеров током этого диода

Следовательно, с этого момента

Из-за того, что динамическое сопротивление транзисторов со стороны эмиттеров носит индуктивный характер, истинной траекторией

30 движения рабочей точки А на фиг. о будет я»ляться траектория е.

Таким образом, при переключениях ТД в цепи эмиттеров транзисторов 1 и 2 действуют скачки тока, а не напряжения, З5 Поскольку все элементы схемы охвачены глубокой токовой связью, а положение нагрузочной линии (кривой) б на фиг. 3 и 5 соответствует одному устойчивому состояьнно, ТД вернется в исходное состояние спустя время l =

40 =1,„с момента поступления входного импульса.

1,„= 6 + t, + t„+ t „ где t„— время возвращения ТД из точки С

45 в точку А (см. фиг. 5).

Учитывая вид траектории движения рабочей точки и вид нагрузочной линии на фиг. 5, можно считать, что 4=1„.

Время возвращения в исходное состояние

50 транзистора 1 с момента поступления входного импульса будет

tT, — 1,;i+ 2t.

Соответственно для транзистора 2

t,, = l„+31., где (2) где t„— время запаздывания коллекторного тока транзисторов относительно эмиттерного тока и связано с процессами диффузии носи60 телей в базе транзистора.

Так как,, изменялся скачком дважды, то в выражение (1) входит 2 l,.

3 1, в выражении (2) связано с тем, что 1,, претерпевал скачки трижды.

65 Рассчеты показывают, что если в схемепри290452 меняются транзисторы с граничной частотой

11000 Мгц, а ТДимеетсобственную емкость

С-5 лф при 1р — — 10 ма, то

t„=4,2 нсек

t,,=4,5 нсек

t„=4,7 нсек

Основная задержка выходных импульсов относительно входного связана со временем l;,.

Если входом служит Вход II, то это время искл юч а ется, и тогда

t,„=1,2 нсек

t„, 1,5 нсек

4, =1,7 нсек.

При необходимости можно получать желаемую длительность выходных импульсов, включая между эмиттерами транзистора 1 и ТД 8 соответствующую индуктивность. Если используется только Вход II схемы, то базу транзистора 1 желательно шунтировать емкостью конденсатора 8.

Амплитудные характеристики схемы легко определяются на фиг. 3 — 6. На импульс, поступивший на Вход 1 схема одновременно отреагирует отрицательным импульсом на коллекгGре транзистора 1 и положительным — на коллекторе транзистора 2.

Таким образом, предлагаемая схема имеет два независимых входа и симметричные вы ioды и может быть применена для построения следующих типов логических элементов:

«ИЛИ», «И», «ИЛИ-НЕ», «И-НЕ», 10 «ИЛИ-ИЛИ-НЕ», «И-И-НЕ», триггер и генератор TBt TOBblx импульсов.

Предмет изобретения

I5 Логический элемент, содержащий р — и — р транзистор, включенный по схеме с общим эмиттером, эмиттер которого соединен с катодом туннельного диода, отлпчаюцийся тем, что, с целью расширения функциональных

20 возможностей и повышения быстродействия элемента, он содержит и — p — и транзистор, включенный по схеме с общей базой, эмнтгер которого соединен с анодом туннельного диода.

290452 .7р (1-о()

<о

dmin (1-Ф)

Фиг 3

7опт

-Е

Фиг 4

Jp (о (/3+1)

7m(n

Фиг. 5 (о(ф„/).

+Ez

Ц1иг б

Составитель А, Д. Федорова

Редактор E. В, Семанова Тскрсд Т. П. Курилко Корректор А, П. Васильева

Изд. № 1GO Заказ 354/12 Тираж 473 Подписное

ЦНИИПИ Комигста по делам пзобрстспий и открытий при Сове с Министров СССР

Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2