Накопитель информации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

292! 94

Савв Советских

Социалистических

Ресаублик

Зависимое от авт. свидетельства М

МПК, б 11с 15, 00

Заявлено 01.VI I.1969 (Л 1341648/18-24) с присоединением заявки М

Приоритет

Опубликовано 06.1.1971. Бюллетень М 4

Дата опубликования описания 26.II.1971

Комитет но делам изобретений и открытий ари Совете Мииистров

СССР

УДК 681.327.02(088.8) I !

Б. Б. Алякринекий и В. В. Наумкенка Б -л *: - —"

Авторы изобретения

Институт автоматики и телемеханики (технической кибернетики) 3 аявитель

НАКОПИТЕЛЬ ИНФОРМАЦИИ

Накопитель информации с последовательной выборкой на триггерах может быть использован в различных системах сбора и переработки информации, в частности, в электронных системах, осуществляющих слежение и сбор информации о каждом обрабатываемом изделии, перемещающемся по технологической линии.

Известны накопители информации, содержащие последовательно соединенные регистры и цепи связи между ними, причем каждый из регистров выполнен на триггерах и содержит цепь сброса регистра в «О».

Предложенное устройство отличается тем, что в нем каждый регистр содержит цепь формирования сигнала состояния регистра, выполненную на элементах «НЕ», «ИЛИ» и элементе задержки, при этом входы элемента

«ИЛИ» соединены с рабочими плечами всех триггеров регистра, а выходы через элемент задержки подключены к цепи сброса в «О» данного регистра и ко входу элемента «НЕ», выход которого соединен с цепью сброса в «О» предыдущего и последующего регистров.

Это упрощает цепи управления при получении плотной записи по регистрам.

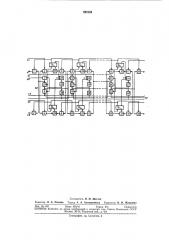

Принципиальная схема накопителя информации показана на чертеже.

Она содержит логические схемы «И» 1 — 22, логические схемы «ИЛИ» 23 — 34, элементы задержки 85 — 87 и логические схемы «НЕ 88—

40.

Накопитель информации содержит и триггерных регистров по !г триггеров в каждом.

5 Каждый регистр имеет логическую цепочку сброса в «О» данного регистра, составленную из логических схем «И» (схемы 7, 8 для первого регистра, 18 — 14 для второго, 21 — 22 для и-го) и «ИЛИ» (схема 28 для первого, 27 для

10 второго, 81 для n-ro), и логическую цепочку формирования сигнала состояния данного регистра, состоящую из последовательно включенных логической схемы «ИЛИ», элемента задержки и логической схемы «НЕ» (схемы

15 2б, 85, 88 для первого, схемы 80, 8б, 89 для второго, схемы 84, 87 и 40 для n-ro), и логических цепочек связи с соседними регистрами из логических схем «И» и «ИЛИ» (1 — б, 24, 25 для первого, 9 — 12, 28, 29 для второго, 15—

20 20, 82, 88 для и-го). Правые рабочие плечи триггера каждого регистра соединены со входами логических схем «ИЛИ» (2б, 80 и 84) цепочек формирова нпя сигналов состояния этих регистров, а левые плечи через логпчеZ5 ские цепочки связи — со входами соответствующих им триггеров в соседних регистрах.

Выходы логических схем «И» (7, 18 и 21) цепочек сброса в «О» любого регистра соединены с логическими схемами «И» (1, 2, 5, б, З0 11 и 12), входящими в цепочки связи этого

292194

45

60 регистра и осуществляющими его связь с регистром, расположенным слева, а входы этих схем (за исключением схемы 7 крайнего левого регистра накопителя) соединены с управляющей шиной 41 переноса влево.

Выходы логических схем «И» (8, 14 и 22) соединены с логическими схемами «И» (9, 10, 15, 16, 19 и 20), входящими в цепочки связи и осуществляющими связь каждого регистра с регистром, расположенным справа, а входы этих схем (за исключением схемы 22 крайнего правого регистра накопителя) соединены с управляющей шиной 42 переноса вправо.

Предположим, что двоичный код хранится в триггерах Тр,, — Tpi, Тогда, поскольку хотя бы на одном из входов логической схемы

«ИЛИ» 26 будет сигнал, то будет сигнал и на выходе этой схемы. При подаче управляющего сигнала на шину 42 в том случае, если регистр (Tp, — Тр,.) свободен, т. е. нет сигнала ни на одной из входных шин логической схемы «ИЛИ» 80, а значит есть сигнал на выходе логической схемы «НЕ» 89, на всех трех входах логической схемы «И» 8 будут сигналы, а следовательно, появится сигнал и на ее выходе. Этот сигнал через логическую схему

«ИЛИ» 28 пройдет на входы всех триггеров первого регистра и сбросит их в «О». Кроме того, этот сигнал пройдет на входы логических схем «И» 9 и 10, благодаря чему возникающие при сбросе регистра импульсы, соответствующие хранимому в регистре коду, поступят на входы триггеров Трг, — Тр,, т. е. осуществляется перенос кода из первого во второй регистр. При этом на выходе элемента

«ИЛИ» 26 сигнал исчезнет, а, значит, через время, определяемое элементом задержки 85, исчезнет и сигнал сброса на выходе элемента

«ИЛИ» 28. На выходе элемента «НЕ» 88 сигнал появится, что означает, что первый регистр свободен. После переноса кода во второй регистр на шине 42 появится сигнал, который через время, достаточное для окончания переходных процессов всех триггеров этого регистра, пройдет на выход элемента задержки 86, а значит и на вход логических схем «НЕ»

89 и «И» 18, 14. При этом на выходе логической схемы «НЕ» 89 сигнал исчезнет, что говорит о занятости данного регистра, а на выходе логической схемы «И» 14 в том случае, если третий регистр свободен, сигнал появится, что приводит к переносудвоичного кода из второго в третий оегистр накопителя информации. Б том случае, если четвертый, пятый, ..., и-й регистры будут свободны, наличие управляющего сигнала на шине 42 приводит к переносу двоичного кода по регистрам слева направо в последний и-й регистр накопителя. В этом регистре код остается, так как нет сигнала на шине 48.

Если теперь в накопитель ввести со стороны входных шин 44, 45 еще какой-либо код и подать сигнал па управляющую шину 42, то, поскольку и-й регистр занят, и значит, нет сигнала на выходе логической схемы «НЕ»

40, который необходим для получения сигнала сброса в «О» триггеров (и — 1)-го регистра, этот код будет перемещаться по регистрам накопителя пока не займет (n — 1)-й регистр.

Следующий код займет (и — 2) -й регистр и т. д, Если же подать сигнал на управляющую шину 41, то все находящиеся в накопителе двоичные коды переместятся влево, заняв крайние левые регистры накопителя. Если затем снять сигнал с шины 41 и подать его на шину 46, то произойдет сброс триггеров

Tp» — Tp<, в «О», а хранящийся в них код поступит через логические схемы «И» 1 и 2 на выходные шины 47 и 48. Для вывода иэ накопителя крайнего правого кода сначала производится сдвиг информации вправо подачей сигнала на управляющую шину 42, а затем — вывод двоичного кода из и-го регистра подачей сигнала на управляющую шину 48.

При вводе информации в накопитель, например, слева, подается сигнал на управляющую шину 42 и после сдвига информации, хранящиеся в накопителе, вправо по сигналу, возникающему. на выходе элемента 88 при освобождении триггеров Тр» — Тр „подается сигнал на шину 49. B результате с входных шин 44, 45 двоичный код в импульсном виде поступает на входы триггеров Тр,, — Тр первого регистра и далее переносится вправо до первого занятого регистра.

Ввод информации в накопитель можно осуществлять сбрасыванием в «О» входных регистров (на чертежах не показаны), так же, как при переносе информации из одного регистра накопителя в другой.

Предмет изобретения

Накопитель информации, содержащий последовательно соединенные регистры и цепи связи между ними, причем каждый из регистров выполнен на триггерах и содержит цепь сброса регистра в «О», отличающийся тем, что, с целью упрощения устройства, каждый регистр накопителя содержит цепь формирования сигнала состояния регистра, выполненную на элементах «НЕ», «ИЛИ» и элементе задержки, при этом входы элемента «ИЛИ» соединены с рабочими плечами всех триггеров: регистра, а выход через элемент задержки. подключен к цепи сброса в «О» данного регистра и к входу элемента «НЕ», выход которого соединен с цепью сброса в «О» предыдущего и последующего регистров.

Составитель В. М. Щеглов

Редактор Л. А. Утехина Техред А. А. Камышникова Корректор В. И. Жолудева

Изд. Ко 167 Заказ 330/10 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2