Устройство для кодирования с адаптацией по разрядности

Иллюстрации

Показать всеРеферат

293239

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Согбз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 07.111.1969 (№ 1323481/18-24) с присоединением заявк:I ¹

Приоритет

Опубликовано 15Л.1971. Бюллетень № 5

Дата опубликования описания 11 V.1971

МП1(G 06f 5/02

Комитет по делам изобретений н открытий при Совете тлннистров

СССР

Ъ ДК 681.325.53(088.8) Автор изобретения

Ю. А. Шикунов

Заявитель

УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ С АДАПТАЦИЕЙ

ПО РАЗРЯДНОСТИ

Изобретение относится к области автоматических систем управления и контроля.

Известны устройства для кодирования процессов с изменяющимся математическим ожиданием во времени, в которых отсутствие априорных данных о характере изменения математического ожидания требует установки максимальной разрядности.

Предлагаемое устройство отличается тем, что в зависимости от характера кодируемого процесса путем предварительного измерения на интервале адаптации математического о>кидания независимых выборов и в зависимости от ео величины подключается определенное количество каскадов таким образом, чтобы точность представления переменной составляющей процесса не изменялась.

Это позволяет получить экономичные по разрядности коды независимо от вида и характера кодируемого процесса.

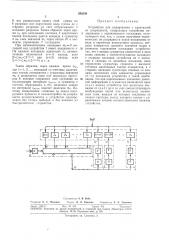

Схема предлагаемого устройства изображена на чертеже.

Оно содержит устройство кодирования 1, состоящее из и информационных и одного знакового каскада (Зн. к), измеритель 2 среднего значения s-разрядных кодов (s(n), состоящий из счетчика 8 адаптивных тактов, сумматора 4, имеющего s входов 5 и знаковый вход

6, элементы управления 7, включаюп;ие логические схемы 8, триггеры 9, s-разрядные входы 10 и выходы 11.

Устройство работает следующим образом.

Длительность входного кодируемого случайs ного процесса Т разбивается на одинаковые пнтерьалы

Т=t,„,+t,,„,+ ....., где t, =t,„.=...

Это разбиение осуществляется автоматически с помощью счетчика 3, управляемого синхроимпульсами. Разрядность счетчика, равная к, определяет величину = УЛ1, где Л = 2", At — дискретность независимых выборок.

Сумматор 4 реализует вычисление алгоритма:

1 Ч ! гг: — Ъу dх., j= I

20 где х, — амплитуда выборок входного процесса; х, . — код х; (s-разрядный); d; — символ знака; пг,, — среднеарифметическое значение з-разрядных кодов на интервале

М

25 Внача -;e вычисляется значение > d õ в

/= I (s — /г)-разрядно;1 сумматоре, а деление на Х (усредненпе) осущесгвляется благодаря тому, что s входов 10 старших разрядов полной

30 суммы кодов постоянно подключены к схемам

293239

Предмет изобретения

Составитель А. В. Вейн

Редактор Б. С. г1анкина Тсхред Л. Л. Евдонов Корректор 3. И. Тарасова

Заказ 1106 11 Изд. № 463 Тира>к 473 Подписн "

11НИИПИ Комитета по делам изобретений и открытий при Совете Министров ССС1

Москва, )К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

8, что равносильно сдвигу этой суммы на

k разрядов или округлению кода суммы до s старших разрядов за счет отбрасывания . г младших разрядов. Таким образом, через время 4, при заполнении счетчика 3 адаптивных тактов последним дается команда в сумматор

4 на съем значения m„ через входы 10 в элементы управления 7 каскадами.

При математическом ожидании т,.=О выходной код устройства 1 имеет разрядность s.

На каждом интервале адаптации t автоматически включается (э+1) каскад, если

2 (т,(2-1 — 1, или (э+2) каскад, если

2-1 — 1(m,.(2-1 — 1) и т. д.

Таким образом, через каждое время где i=1, 2 ...., командой со счетчика адаптивных тактов считывается с сумматора значение т„и включается один или несколько триггеров 9, которые сохраняют свое состояние на последующем интервале 11; ь а сумматор и счетчик, сбрасываясь в «0», начинают заново на интервале l„1;1ц подсчет значения т,. Поэтому кодирование, слежение за видом кодируемого процесса и самонастройка по разрядности осуществляются в устройстве одновременно без потерь выборок и без влияния на быстродействие устройства.

Устройство для кодирования с адаптацией по разрядности, содержащее устройство ко5 дирования с управляемыми каскадами, отличаюи1ееся тем, что, с целью получения экономических по разрядности кодов независимо от вида и характера кодируемого процесса, введены измеритель среднего значения кодов и

10 элементы управления каскадами устройства так, что s входов сумматора измерителя и вход знака связаны с соответствующими выходами

s старших каскадов устройства из и каскадов и связаны со знаковым каскадом; вход

15 управления сумматора соединен с выходом счетчика адаптивных тактов измерителя, а s старших каскадов сумматора связаны со входами логических схем элементов управления (n — s) каскадами устройства в такой комби20 нации, что при определенных значениях двоичной информации в сумматоре включается один (s+1) каскад устройства или несколько каскадов от (s+I) до и за счет соответствующего возбухкдения одной пли нескольких логиче25 ских схем, каждая из которых соединена со входом триггера, выход которого связан с управляемым входом соответствующего каскада устройства.