Динамический элемент на мдп-транзисторах

Иллюстрации

Показать всеРеферат

294252

О П И С А Н И Е

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сей)в Советских

Социалистических

Реслублин

Зависимое от авт. свидетельства №

Заявлено 12.11.1970 (№ 1404378/18-24) с присоединением заявки №

Приоритет

Опубликовано 26.I.1971. Бюллетень № 6

Дата опубликования описания 24.III.1971

МПК Н 03jc 17/66 комитет ло делам изобретений и открытий лри Совете Министров

СССР

УДК 681.325.65(088.8) I Р EC ..2 -зз ).

;! й," 2,., .» "", iËÿ

А. Н. Кармазинский, Г. й. Назарин и В. И. (Шагрризй е-.

Авторы изобретения

Заявитель

Московский инженерно-физический институт

ДИНАМИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ

Изобретение относится к области автоматики и вычислительной техники и предназначено для построения интегральных логических схем с высоким быстродействием и малой потребляемой мощностью.

Известен динамический элемент на МДПтранзисторах, в котором цепь разряда запоминающего конденсатора выполнена на двух транзисторах, в результате чего время разряда конденсатора ограничивает быстродействие элемента и требует увеличения размеров транзисторов цепи разряда.

Предложенное устройство отличается тем, что цепь разряда запоминающего конденсатора выполнена на одном транзисторе, с затвором которого соединен исток вспомогательного транзистора.

Это позволяет повысить быстродействие элемента и уменьшить размеры используемой полупроводниковой пластины.

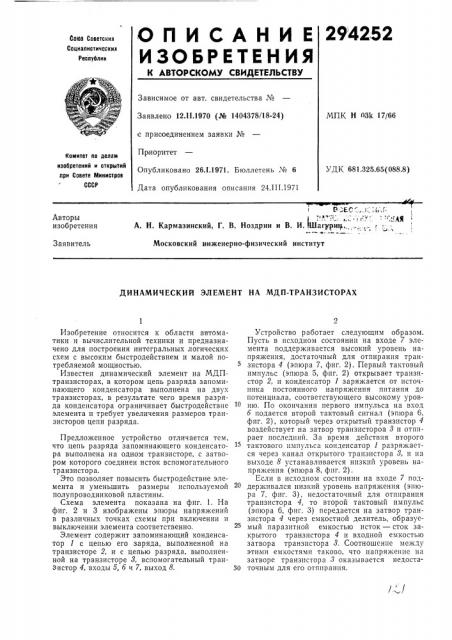

Схема элемента показана на фиг. 1. На фиг. 2 и 3 изображены эпюры напряжений в различных точках схемы при включении и выключении элемента соответственно.

Элемент содержит запоминающий конденсатор 1 с цепью его заряда, выполненной на транзисторе 2, и с цепью разряда, выполненной на транзисторе 8, вспомогательный транзистор 4, входы 5, 6 и 7, выход 8.

Устройство работает следующим образом.

Пусть в исходном состоянии на входе 7 элемента поддерживается высокий уровень напряжения, достаточный для отпирания транзистора 4 (эпюра 7, фиг. 2). Первый тактовый импульс (эпюра 5, фиг. 2) открывает транзистор 2, и конденсатор 1 заряжается от источника постоянного напряжения питания до потенциала, соответствующего высокому уровню. По окончании первого импульса на вход б подается второй тактовый сигнал (эпюра 6, фиг. 2), который через открытый транзистор 4 воздействует на затвор транзистороа 3 и отпирает последний. За время действия второго тактового импульса конденсатор 1 разряжается через канал открытого транзистора 8, и на выходе 8 устанавливается низкий уровень напряжения (эпюра 8, фиг. 2).

Если в исходном состоянии на входе 7 поддерживался низкий уровень напряжения (эпюра 7, фиг. 3), недостаточный для отпирания транзистора 4, то второй тактовый импульс (эпюра 6, фиг. 3) передается на затвор транзистора 4 через емкостной делитель, образуемый паразитной емкостью исток — сток закрытого транзистора 4 и входной емкостью затвора транзистора 3. Соотношение между этими емкостями таково, что напряжение на затворе транзистора 3 оказывается недоста30 точным для его отпирания.

294252

Предмет изобретения

Фиг 1

Фиг Z

Фиг,У

Составитель В. Игнатущенко

Редактор Ю. Полякова Техред Л. Я. Левина Корректор О. М. Ковалева

I!çë. № 278 Заказ 622/7 Тираж 473 Подписное

ЦН11ИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4j5

Типография, пр. Сапунова, 2

Поэтому цепь разряда конденсатора 1 остается разомкнутой, и на выходе 8 поддерживается высокий уровень напряжения (эпюра 8, фиг. 3). Таким образом, за время цикла происходит инверсия входного сигнала.

Подсоединяя последовательно и параллельно транзистору 4 другие транзисторы, можно придавать элементу те или иные логические функции. При использовании четырехфазной системы питания элемент образует функционально полную систему.

Динамический элемент на МДП-транзисторах, содержащий запоминающий конденсатор и цепи его заряда и разряда, а также вспомогательный транзистор, отличающийся тем, что, с целью повышения быстродействия и уменьшения площади используемой полупроводниковой пластины, цепь разряда запоминающего конденсатора выполнена на одном транзисторе, с затвором которого соединен исток вспомогательного транзистора.