Быстродействующая интегральная транзисторно- транзисторная логическая схема

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 294253

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

МПК Н 03k 19/00

Заявлено 20.Х.1969 (№ 1370103/18-24) с присоединением заявки №

Приоритет

Опубликовано 26.1.1971. Бюллетень № 6

Дата опубликования описания 24.I I I.1971

Комитет по делам изобретений и открытиЯ при Совете Министров

СССР

УДК 681.325.65(088.8) Автор изобретения

В. В. Шагалин

Заявитель

БЫСТРОДЕЙСТВУЮЩАЯ ИНТЕГРАЛЬНАЯ ТРАНЗИСТОРНОТРАНЗИСТОРНАЯ ЛОГИЧЕСКАЯ СХЕМА

Изобретение относится к автоматике и вычислительной технике.

Известна быстродействующая интегральная транзисторно-транзисторная логическая схема, в которой для уменьшения задержки выключения параллельно коллекторному переходу транзисторов включают диоды Шоттки.

В этой схеме шунтирование коллекторного перехода выходного транзистора диодом

Шоттки хотя и ускоряет рассасывание, но повышает напряжение на выходе открытой схемы, в результате чего ухудшается ее помехоустойчивость.

При поступлении на все входы схемы нулевого сигнала база выходного транзистора оказывается изолированной от входа. Поэтому эмиттерный переход выходного транзистора шунтируется резистором, что снижает отпирающий сигнал на базе этого транзистора при приходе «единичного» входного сигнала и, следовательно, увеличивает время включения транзистора.

Цель изобретения заключается в повышении быстродействия ТТЛ схемы без ухудшения остальных ее статических и динамических параметров. Она достигается соединением базы выходного транзистора со входами схемы через диоды Шоттки. Таким образом удается уменьшить сопротивление цепи, по которой протекает базовый рассасывающий ток выходного транзистора, в результате чего ускоряется его рассасывание, а следовательно и задержка выключения всей схемы.

Так как прп наличии единичного сигнала на одном из входов схемы база выходного транзистора оказывается подключенной к этому в. оду через открытый диод Шотткп, то отпадает необходимость в шунтировании эмиттерного перехода выходного транзистора.

Поэтому ускоряется включение выходного транзистора.

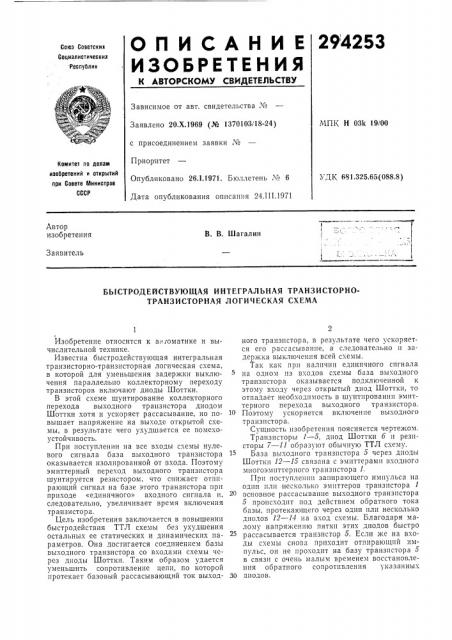

Сущность изобретения поясняется чертежом.

Транзисторы 1 — 5, диод Шоттки б и резисторы 7 — 11 образуют обычную ТТЛ схему.

База выходного транзистора 5 через диоды

Шоттки 12 — 15 связана с эмиттерамп входного мпогоэмиттерного транзистора 1.

Прп поступлении запирающего импульса на один илп несколько эмиттеров транзистора 1 основное рассасывание выходного транзистора

5 происходит под действием обратного тока базы, протекающего через один или несколько диодов 12 — 14 на вход схемы. Благодаря малому напряжению пятки этих диодов быстро рассасывается транзистор 5. Если же на входы схемы снова приходит отпирающий импульс, он не проходит на базу транзистора 5 в связи с очень малым временем восстановления обратного сопротивления указанных

30 диодов.

294253

Составитель Д. Голубович

Текред Л. Я. Левина Корректор О. М. Ковалева

Редактор Б. Б. Федотов

Изд. Ко 278 Заказ 62278 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Таким образом, оказывается возможным получить весьма быстродействующую ТТЛ схему, имеющую малые задержки как включения, так и выключения и имеющую высокую помехоустойчивость.

Предмет изобретения

Быстродействующая интегральная транзисторно-транзисторная логическая схема

«ИЛИ вЂ” НЕ» («И — НЕ»), содержащая входной многоэмиттерный транзистор и инвертор на четырех транзисторах, отличающаяся тем, что, с целью увеличения быстродействия, она содержит диоды Шоттки, причем катод каждого из диодов подключен к одному из входов схемы, а аноды объединены и соединены с базой выходного транзистора.