Способ управления цифровым интегратором

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 295285

ИЗОБРЕТЕНИЯ

Воюа Советских

Социалистических

Республик

К П А ТЕНТУ

Зависимый от патента №

MHK G 06) 1/02

Заявлено 07.Ч.1966 (№ 1074886/26-24) Приоритет

Комитет по делам изобретений н открытий при Совете Министров

СССР

Опуоликовапо 04.11.1971. Вюллетеш. № 7

УДК 681.332.64(088.8) Дата опубликования описания 6.1Ч.1971

Лвторы изобретения

Иностранцы

Бернар Лувел и Анри Альберни (Франция) Иностранная фирма

«Сосьете Насиональ де Петроль д Акитэн» (Франция) Заявитель

СПОСОБ УПРАВЛЕНИЯ ЦИФРОВЫМ ИНТЕГРАТОРОМ

Известен способ управления цифровым интегратором, основанный на формировании сигнала запуска интегратора путем обнаружения превышения интегрируемого сигнала над заданным опорным уровнем.

Предложенный способ отличается от известного тем, что анализируют результат сравнения числа импульсов, полученных путем предварительного преобразования интегрируемого сигнала в частоту их следования и подсчитанных за последовательные определенные интервалы времени, с наперед заданным числом и в зависимости от знака разности формируют разрешающий или запрещающий сигнал, используемый для управления входной вентильной схемой интегратора.

Это позволило повысить точность интегрирования.

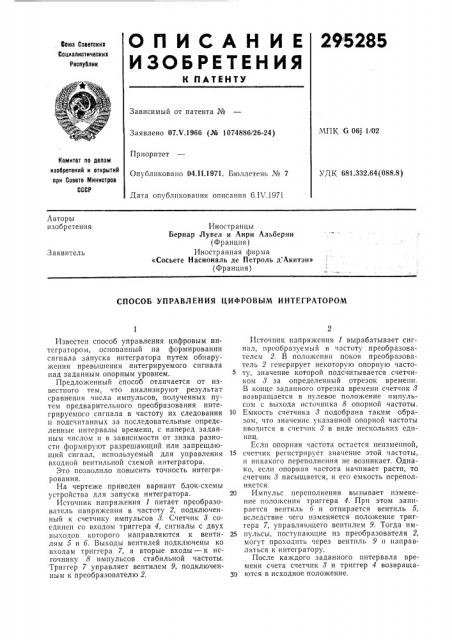

На чертеже приведен вариант блок-схемы устройства для запуска интегратора.

Источник напряжения 1 питает преобразователь напряжения в частоту 2, подключенный к счетчику импульсов 8. Счетчик 8 соединен со входом триггера 4, сигналы с двух выходов которого направляются к вентилям 5 и 6. Выходы вентилей подключены ко входам триггера 7, а вторые входы — к исгочнику 8 импульсов стабильной частоты.

Триггер 7 управляет вентилем 9, подключенным к преобразователю 2.

Источник напряжения 1 вырабатывает сигнал, преобразуемый в частоту преобразователем 2. В положении покоя преобразователь 2 генерирует некоторую опорную частоту, значение которой подсчитывается счетчиком 3 за определенный отрезок времени.

В конце заданного отрезка времени счетчик 8 возвращается в нулевое положение импульсом с выхода источника 8 опорной частоты.

10 Емкость счетчика 8 подобрана таким образом, что значение указанной опорной частоты вводится в счетчик 8 в виде нескольких единиц.

Если опорная частота остается неизменной, 15 счетчик регистрирует значение этой частоты, и никакого переполнения не возникает. Однако, если опорная частота начинает расти, то счетчик 3 насыщается, и его емкость переполняется.

20 Импульс переполнения вызывает изменение положения триггера 4. При этом запирается вентиль 6 и отпирается вентиль 5, вследствие чего изменяется положение триггера 7, управляющего вентилем 9. Тогда им25 пульсы, поступающие из преобразователя 2, могут проходить через вентиль 9 и направляться к интегратору.

После каждого заданного интервала времени счета счетчик 8 и триггер 4 возвраща30 ются в исходное положение, 295285

Г ) о

Предмет изобретения

Соетавителв Л. Л. Маелов

Техред Е. Ьорисова Корректор Л. A. Царькова

Редактор Л. Л. Утехина

Заказ 788/13 Изд, J¹ 3J6 Тирахк 473 Подпиепое

ЦНИИПИ Комитета по делам изобретеиий и открытий при Совете Миииетров СССР

Москва, 7К-35, Раугиекаи иаб., д. 4/5

Типографии, ир. (аиуиова, 2

Способ управления цифровым интегратором, основанный на формировании сигнала запуска интегратора путем обнарухкения превышения интегрируемого сигнала над заданным опорным уровнем, отличи)осцийсл тем, что, с целью повышения точности интегрирования, анализируют результат сравнения чпсла импульсов, полученных путем предварительного преобразования интегрируемого сигнала в ":àñòîòó их следования и подсчитанных за последователь ые определенные интервалы времени, с наперед заданным числом и в зависимости от знака разности формируют разрешающий пли запрещающий сигнал, используемый для управления входной вснтильной схемой интегратора.