Гибридное вычислительное устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Рвсптблик

Зависимое от авт. свидетельства №

МПК С О61 1/ОО

Заявлено 22.XII.1969 (№ 1387158/18-24) с присоединением заявки ¹

Приоритет

Комитет по делам изобретений и открытий при Совете тлинистров

СССР

Спубликовапо 11.Ill.1971. Бюллетень № 1О

Дата опубликования описания 10Х.1971

УДК 681.З4.О(О88.8) Авторы изобретения

Г. Е. Пухов, В. В. Аристов и В. Д. Самойлов

Институт кибернетики AH Украинской ССР

Заявитель

Г, л, ГИБРИДНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники.

Известны гибридные вычислительные устройства, содержащие соединенные между собой цифровой автомат, динамический коммутатор, блок релейных переключателей, устройство автономного у равновсшивания, преобразователь напря?кение †к и квазианалоговое устройство.

Сднако известные устройства имеют ограниченный класс решаемых задач и требуют больших аппаратурных затрат.

Б предложенном устройстве эти недостатки устранены.

Устройство отличается от известных тем, что оно содеp?KHT матрицы запоминающих модуляторов старших и младших разрядов коэффициентов, преобразователи старших и младших разрядов пространственно-импульсного кода в фаза-импульсный и адресные регистры, причем квазианалоговое устройство выполнено в виде матрицы переключаемых резисторов, соединенной с матрицами запоминающих модуляторов старших и младших разрядов коэффициентов, ка?кдая из которых через общие адресные регистры и преобразователи старших и младших разрядов пространственноимпульсного кода в фазо-импульсный соединена с выходами цифрового автомата.

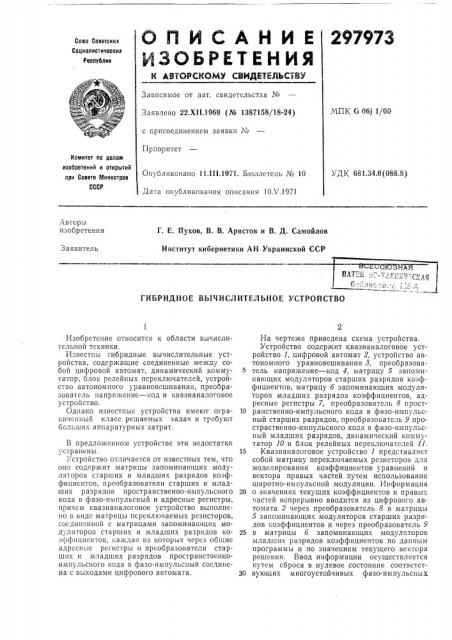

На чертеже приведена схема устройства.

Устройство содержит квазианалоговое устройство 1, цифровой автомат 2, устройство автономного уравновешивания 8, преобразователь напряжение — код 4, матрицу 5 запоминающих модуляторов старших разрядов коэффициентов, матрицу б запоминающих модуляторов младших разрядов коэффициентов, адресные регистры 7, преобразователь 8 прост10 ранственно-импульсного кода в фазо-импульсный старших разрядов, преобразователь 9 простраственно-импульсного кода в фазо-импульсный младших разрядов, динамический коммутатор 10 и блок релейных переключателей 11.

15 Квазианалоговое устройство 1 представляет собой матрицу переключаемых резисторов для моделирования коэффициентов уравнений и вектора правых частей путем использования широтно-импульсной модуляции. Информация

20 о значениях текущих коэффициентов и правых частей непрерывно вводится из цифрового автомата 2 через преобразователь 8 в матрицы

5 запоминающих модуляторов старших разрядов коэффициентов и через преобразователь 9

25 в матрицы б запоминающих модуляторов младших разрядов коэффициентов по данным программы и по значениям текущего вектора решения. Бвод информации осуществляется путем сброса в нулевое состояние соответстЗО вующих многоустойчивых фазо-импульсных

297973

Составитель Г. К. Сорокин

Редактор Jl. А. Утехина Техред Л. Л. Евдонов Корректор О. И. Волкова

Заказ 1157/9 Изд. № 501 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д, 4/5

Типография, пр. Сапунова, 2 (3 элементов матриц 5 и б, определяемых кодом адресных регистров 7, в моменты времени, соответствующие выходным импульсам преобразователей 8 и 9. Импульсы многоустойчивых фазо-импульсных элементов через логические схемы и управляющие триггеры (на черте кс не показаны) управляют ключами аналоговых сигналов, коммутирующих резисторы квазианалогового устройства 1 со скважностью, пропорциональной величине соответствующсго коэффициента.

Устройство автономного уравновешивания 3 демодулирует широтно-импульсные сигналы из квазианалогового устройства 1, преобразуя их в непрерывный вектор решения, все или часть компонентов которого поступают через динамичсский коммутатор 10 и преобразователь напряжение — код 4 в цифровой автомат 2 для вычисления необходимых нелинейных коэффициентов.

Перед началом решения с помощью блока релейных переключателей 11 производится набор структуры квазианалогового устройства 1 и устройства автономного уравновешивания 8 и устанавливаются необходимые начальные условия.

Через каналы связи 12 и 13 устройства может быть произведен обмен информацией с оператором и с различными устройствами.

Предмет изобретения

Гибридное вычислительнос устройство, содержащее соединенные между собой цифровой автомат, динамический коммутатор, блок релейных переключателей, устройство автоном10 ного уравновешивания, преобразователь напряжение — код и квазианалоговое устройство, отличаюи ееся тем, что, с целью расширения класса решаемых задач и упрощения устройства, оно содержит матрицы запоминающих

15 модуляторов старших и младших разрядов коэффициентов, преобразователи старших и младших разрядов пространственно-импульсного кода в фазо-импульсный и адресные регистры, причем квазианалоговое устройство

20 выполнено в виде матрицы переключаемых резисторов, соединенной с матрицами запоми,ающих модуляторов старших и младших разрядов коэффициентов, каждая из которых через общие адресные регистры и преобразова25 тели старших и младших разрядов пространственно-импульсного кода в фазо-импульсный соединена с выходами цифрового автомата.