Логическая схема с регулируемым порогом12

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 299076

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К ПА ГЕНТУ

Зависимый от патента Xe—

Заявлено 09.1.1969 (№ 1300347/18-24)

Приоритет 09.1.1968, № 135311, Франция

МПК G 0617/04

Комитет по делам изобретений и открытий прн Совете Министров

СССР

УДК 681.325.65(088.8) Бюллетень М 11

Опубликовано.

Дата опубликования описания

В С EC0 Ñ 3 г-i.-"Ë

БИБЛИОТЕКА

Автор изобретения

Иностранец

Жак Луи Сован (Франция) Иностранная фирма

«Сосьете Насьональ д Этюд э де Констрюксьон де Мотор д Авиасьон Снэкма» (Франция) Заявитель

ЛОГИЧЕСКАЯ СХЕМА С РЕГУЛИРУЕМЫМ ПОРОГОМ

Изобретение относится к логическим схемам, которые могут быть использованы для вычислительных, у правляющих и регулирующих устройств дискретното действия в области автоматики и вычислительной техники.

Известны логические схемы в виде прямоугольных матриц, содержащие элементы «И», «ИЛИ» и ин:верторы.

Целью изобретения является реализация логической схемы с регулируемым порогом, обладающей достаточной простотой .и широкими функциональными возможностями.

Указанная цель достигается путем использования матрицы, на пересечении строк и столбцов которой включены цепи блокировки, а,на их выходе — цепь сравнения групп входных сигналов.

Цепь блокировки выполнена на трех элементах «И», каждый из которых имеет два общих входа с двумя соседними элементами, а между выходом одного из элементов и общим входом двух других включен инвертор.

Цепь сравнения группы входных сипналов выполнена на элементах «ИЛИ», один из которых связан со всеми выходными шинами столбцов матрицы, а другой — со всеми выход ными шинами строк матрицы, причем выходы двух элементов «ИЛИ» соединены со входами третьего элемента «ИЛИ», а |послед,ний, в свою очередь, — с инвертором.

Кроме того, логическая схема содержит минимальное число цепей блокировки. Она имеет две вспомогательные цепи, выполненные на элементах «И» и «ИЛИ», причем в одной

5 цепи первый вход элемента «И» соединен с входной щи|ной строки матрицы, второй вход — с выходной шиной той же стропи матрицы через инвертор, а в другой цепи каждый вход элемента «ИЛИ» соединен с входом

10 одного из инверторов, принадлежащих цепям блокировки одной,и той же строки матрицы.

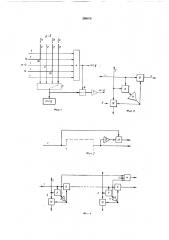

На фиг. 1,приведена логическая схема с переменным порогом; на фиг. 2 — цепь блоки15 ровни; на фиг. 3 и 4 — вспомогательные цепи; на фиг. 5 и 6 — работа логической схемы с переменным порогом; на фиг. 7 — условия, при которых может быть сокращено число цепей блокировки.

20 Логическая схема с переменным порогом содержит и входов I, представляющих собой строки матрицы, Р пороговых входов 2— столбцы матрицы, на,пересечении которых включены цепи блокировки 8.

25 Выход каждой строки матрицы соедтвнен с соответствующим входом элемента 4, а выход каждого столбца — с соответствующим входом элемента 5. Элементы 4 — 6 являются элементами «ИЛИ» (выходы элементов 4 и 5 со30 единены со входами элемента 6) . В свою

299076 очередь выход элемента б соединен со входом и нвертора 7.

Цепь блокировки 8 (см. фиг. 2) состоит из трех элементов «И» 8 — 10, каждый из |которых имеет два общих с двумя соседними элементами входа, а между выходом элемента

«И» 9 и общим входом элементов «И» 8 и 10 включен инвертор 11.

Вспомогательная цепь (см. фиг. 3) состоит из элемента «И» 12, один из входов которого соединен с входом 1 матрицы, а второй вход — с выходной ш иной той же страки через инвертор 18.

Другая вспомогательная цепь (см. фиг. 4) состоит из элемента «И» 14, каждый вход которого соединен с входом од ного из инверторов

11, принадлежащих цепям блокировки одной и той же стр оки м атр и цы.

Логическая схема с переменным порогом работает следующим образом.

P е ж и м 1. Если два входа 1а и 1в:возбуждены, а так же воз буждены три пороговых входа 2а, 2в и 2с, то цепи блокировки 8а и 8в ограничат прохождение входных сигналов с возбужденных входов 1а, 1в, 2а, 2в на элементы 4 и 5. Когда входы элемента «И» 9 возбуждены, то возбуждается вход инвертора И, а общий вход элементов «И» 8 и 10, связанный с выходом инвертора 11, остается не возбужденным, и сигналы блокируются.

Следовательно, только возбужденный вход

2с пройдет на элемент 5, и на выходе элемента

5 появится сигнал, который показывает, что число возбужденных входов т меньше числа возбужденных пороговых входов q(m

Если число возбужденных входов равно числу,возбужденных пороговых |входов, то цепи блокировки ограничат, прохождение сигналов на элементы 4 и 5, что приведет к отсутствию сигналов на:входах элемента 6. Следовательно, на выходе инвертора 7 появится сигнал, который показывает, что число возбужденных входов т не.равно числу возбужде|нных пороговых входоэ q(m=q).

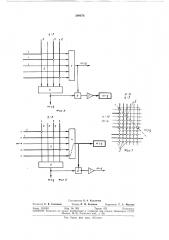

Логическая схема с переменным по рогом работает независимо от порядка возбуждения .входов, однако, если такой порядок будет соблюдаться и пороговые входы будут возбуждаться слева направо (см. фиг. 7), то число цепей блокировки может быть уменьшено ,Р— Р на величину 2, и общее число цепей бло ) кировки будет

Логическая схема с переменным порогом включает в себя варианты вспомогательных цепей, одна из которых приведена на фиг. 3, а другая на фиг. 4.

Вспомогательные цепи позволяют получить сигналы возбужденных входов, задержанные цепями блокировки. Одна из них состоит из элемента «И» 12 и и нвертора 18. На выходе элемента «И» 12 появляется сигнал только в том случае, если вход 1 возбужден и блоки рован цепью блокировки 8 внутри матрицы.

Вторая вспомогательная цепь состоит из элемента «ИЛИ» 14, входы которого соеди15 иены с входом .каждого инвертора 11, принадлежащего одной и той же строке.

Вторая вспомогательная цепь выполняет те же функции, что и первая.

Предмет изобретения

1. Логическая схема с регулируемым порогом, представляющая прямоугольную матрицу, содержащая элементы «И», «ИЛИ» и

25 инверто ры, отличающаяся тем, что, с целью упрощения и повышения функциональных возможностей, на пересечении строк и столоцов матрицы включены цепи блокировки, а на их выходе — цепь сравнения групп входных сигналов.

2. Схема,по п. 1, отличающаяся тем, что цепь блокировки выполнена на трех элементах «И», каждый из которых имеет два общих входа с двумя соседними элементами, а меж35 ду выходом одного из элементов и общим входом двух других включен инвертор.

3. Схема по п. 1, отличающаяся тем, что цепь сравнения групп входных сигналов выполнена на элементах «ИЛИ», один из которых

0 связансо всеми выходными шинами столбцов матрицы, а другой со всеми выходными шинами строк матрицы, причем выходы двух элементов «ИЛИ» соединены со входами третьего элемента «ИЛИ», а .последний, в свою оче45 редь, с инвертором.

4. Схема iso:п. I, отличающаяся тем, что она содержит две вспомогательные цепи, выполнен ные на элементах «И» и «ИЛИ», .причем в одной цепи первый вход элемента «И» соединен с входной щи ной строки матрицы

7 второи вход — с выходной шиной той же строки матрицы через инвертор, а в другой цепи каждый вход элемента «ИЛИ» соединен с входом одного из инверторов, принадлежа55 щих цепям блокировки однои и той же строки матрицы.

299076,г 2 I Z

Ф(Фиг и

Составитель Б. A. Каключин

Техред Л. П. Евдонов Корректор Г. С. Мухина

Редактор Е. В. Семанова

Тип, Харьк. фил, пред. «Патент»

Заказ 129/491 Изд. № 353 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5