Устройство задержки импульсов

Иллюстрации

Показать всеРеферат

О П И СА Н И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

30I838

Союз Советских

Социалистических

Реслтблик

Зависимое от авт. свидетельства №

Заявлено 30.11!.1970 (№ 1420435/18-24) с присоединением заявки ¹

Приоритет

Опубликовано 21.IV.1971. Бюллетень № 14

Дата опубликования описания 4.VI.1971

МПК Н 031 5, 00

Комитет ос делам изаоретвиий и открмтий ори Совете Министров

СССР

УДК 681.3.055 (088.8) Авторы изобретения

Г. Я. Мирский и H. Д. Автонов

Заявитель

УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ

Предлагаемое устройство относится к области специализированных средств вычислительной техники.

Известно устройство задержки импульсов, содержащее регистры сдвига, генератор продвигающих импульсов, дифференцирующую цепочку и триггер.

Недостатком такого устройства является то, что задержка на большие интервалы импульса, приходящего в случайный момент времени, сопровождается значительной погрешностью.

Для получения малой погрешности требуется существенное увеличение частоты следования продвигающих импульсов, что влечет за собой при больших задержках значительное увеличение числа триггеров в регистре.

С целью повышения точности работы предлагаемое устройство содержит матрицу, дополнительно триггер и вентиль, а также вспомогательную пересчетную схему, вход которой соединен с выходом вентиля, подключенного через единичный выход триггера к выходу вспомогательной пересчетной схемы, нулевой вход указанного триггера связан со входной шиной устройства, выходы вспомогательной пересчетной схемы через матрицу соединены с выходами устройства.

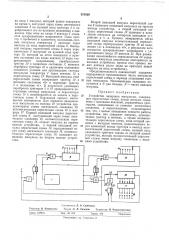

На чертеже представлена функциональная схема предлагаемого устройства.

В этой схеме вход 1 устройства соединен через первую схему логического сложения 2 с нулевым входом триггера 8, единичный выход которого подключен ко входу 4 вентиля 5, а вход б этого вентиля связан с выходом гене5 ратора 7 счетных импульсов. Выход вентиля 5 подключен ко входу пересчетной схемы 8, выход которой присоединен через переключатель

9 к нулевому входу триггера 10. Единичный выход триггера 10 подключен ко входу 11 вен10 тпля 12, входом связанного с выходом генератора 7 счетных импульсов. Выход вентиля 12 соединен со входом пересчетной схемы 13. Ес выход, в свою очередь, подключен посредством переключателя 14 к единичному входу трпгге15 ра 10, ко входу схемы логического сложения

15 и ко входу схемы логического сложения 2.

Выход схемы логического сложения 15 подключен через вспомогательную пересчетную схему 16 и матрицу 17 к выходам 18 устрой20 ства. Выход вспомогательной пересчетной схемы 1б соединен с единичным входом трпггера

19, единичный выход которого подключен к управляющему входу 20 вентиля 21, присоединенного сигнальным входом 22 к выходу схе25 мы логического сложения 15, а выходом — ко входу вспомогательной пересчетной схемы 1б, нулевой вход триггера 19 соединен со входом

1 устройства

Устройство раоотает следующим образом.

30 Приходящий в случайный момент времени

301838

Составитель Л. В. Скобелева

Редактор В. Новоселова Текрсд Л. Л. Евдонов Корректор Н. Рождественская

Тираж 473

Изд. 1Чв GI9

Подписное

Заказ 1370/11

Типография, пр. Сапунова, 2 на вход 1 импульс, который нужно задержать на время т, поступает через схему логического сложения 2 на нулевой вход триггера 8 и перебрасывает его из нулевого положения в единичное. При этом на входе 4 вентиля 5 создается «разрешающее» напряжение. Пока триггер 8 пребывает в единичном положении, счетные импульсы генератора 7 проходят через вентиль на вход пересчетной схемы 8. Выходной импульс пересчетной схемы 8 через переключатель 9 поступает на нулевой вход триггера 10, который до этого находился в нулевом состоянии (на входе вентиля 12 было «запрещающее» напряжение), перебрасывает триггер 10 в единичное состояние. С момента переброса триггера 10 в единичное положение создаются условия для прохождения счетных импульсов генератора 7 через вентиль 12 в пересчетную схему 18. Выходной импульс этой пересчетной схемы возвращает триггер 10 в исходное состояние «0» и переводит триггер

8 в положение «1». В результате указанных перебросов триггеров 8 и 10 прекращается поступление счетных импульсов в пересчетную схему И и возобновляется их подача в пересчетную схему 8. Описанный процесс многократно повторяется. Для передачи задержанных импульсов на выходы 18 устройства предусмотрены схемы логического сложения 15, вспомогательная пересчетная схема 1б и матрица 17. Первый выходной импульс пересчетной схемы 8, поступающий через схему логического сложения 15, вспомогательную пересчетную схему 1б, создает импульс на первом выходе устройства, а первый выходной импульс пересчетной схемы И, передаваемый через схему логического сложения 15, вспомогательную пересчетную схему 1б, вызывает появление импульса на втором выходе устройства.

Второй выходной импульс пересчетной схемы 8 вызывает появление импульса на третьем выходе устройства, а второй выходной импульс пересчетной схемы И приводит к появ5 лению импульса на четвертом выходном устройстве и т; д. Процесс завершается, когда выходной импульс вспомогательной пересчетной схемы перебрасывает триггер 19 из положения «1» в положение «0», в результате чего

10 снимается «разрешающее» напряжение с управляющего входа 20 вентиля 21. При размыкании однолинейного переключателя 28 задержанные импульсы циклически повторяются:на выходах устройства, причем этот процесс мо15 жет длиться долго (если не приходит новый импульс на вход устройства).

Продолжительность однократной задержки определяется произведением числа импульсов пересчетной схемы и периода следования счет20 ных импульсов. Максимальная задержка получается в N раз больше. N — число выходов матрицы.

Предмет изобретения

25 Устройство задержки импульсов, содержащее пересчетные схемы, входы которых соединены с выходами вентилей, управляемых триггерами, связанными со схемами логического сложения, и переключатели, отличающееся

З0 тем, что, с целью повышения точности работы устройства, оно содержит матрицу, дополнительно триггер и вентиль, а также вспомогательную пересчетную схему, вход которой соединен с выходом вентиля, подключенного чеЗ5 рез единичный выход триггера к выходу вспомогательной пересчетной схемы, нулевой вход указанного триггера связан со входной шиной устройства, выходы вспомогательной пересчетной схемы через матрицу соединены с выхо40 дами устройства.