Импульсный синхронизатор

Иллюстрации

Показать всеРеферат

и о т;.

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

30!856

Союз Советокиз

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 28.Х.1968 (№ 1278197/26-9) с присоединением заявки №

Приоритет

Опубликовано 21.1Ъ .1971. Бюллетень ¹ 14

Дата опубликования описания 13ХП.1971,ЧПК Н 031(19/42

Комитет по делам изобретений и открытий при Сосете Министров

СССР

УДК 621.373.43 (088.8) Автор изобретения

О. Ф. Черепов

Заявитель

ИМПУЛ ЬСН ЫЙ СИ НХРО Н И ЗАТО Р

Изобретение относится к области вычислительной техники, автоматике и телемеханике и может быть использовано в системах обработки данных, поступающих с датчиков, контролирующих работу автоматической системы.

Известные импульсные синхронизаторы, содержащие три инвертора, два элемента

«ИЛИ» и четыре элемента «И», не обеспечивают синхронизации и однозначной передачи входных сигналов при любых комбинациях совпадения во времени входного и тактового импульсов.

С целью исключения потери информации и появления на выходе помехи в предлагаемом импульсном синхронизаторе между его сигнальным входом и выходным элементом

«И» включены инвертор и логическая схема запоминания, выполненная на двух элементах

«ИЛИ» и одном элементе «И»; логическая схема списывания, содержащая инвертор, элементы «ИЛИ» и «И», подключена к логической схеме запоминания и третьему входу выходного элемента «И».

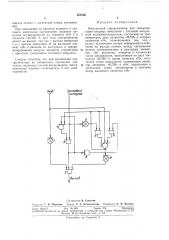

На чертеже приведена функциональная схема предлагаемого устройства.

Предлагаемое устройство работает следующим образом.

Если на синхронизатор первым приходит сигнальный импульс, то он поступает через ипвертор 1 на выходной элемент «И» 2 и одповременно на элемент «ИЛИ» 8, а с выходя последнего на элемент «ИЛИ» 4. Поскольку в данный момент тактовый импульс отсутствует, то с инвертора 5 поступает сигнал ня

5 элемент «ИЛИ» 4, который выдает сигнал ня элемент «И» 8, в результате чего обеспечивается запоминание входного импульса после его пропадания.

Поступление тактового импульсtt вызывяе?

10 появление сигнала на выходе элемент;l «11»

6, который поступает .?а выходной элеме1?т

«И» 2, на самоблокировку через элемент

«ИЛИ» 7 и через повторитель 8 на элемент

«ИЛИ» 9. Таким образом, функции запом?гна15 ния выполняет логическая схема, собранная па двух элеменгах «ИЛИ» 4 и 9 и а элементе «И» 3, а функции списывания выполняет логическая схема, выполненяя ня пнвсрторе 5, элементе «ИЛИ» 7 и элементе «11» 6.

Одновременно при ??олуплегп?п тактового импульса с инвертора 5 перестает поступать сигнал па элемент «ИЛИ» 4, что вызы????е? появление на выходе ипвертора 10 сигнала,tt(?25 ступающего на выходной элемент «И» 2, который выдает синхронизированный импульс.

Повторитель 8 служит в качестве задержки на время срабатывания, по крайней мере, двух логических элементов «ИЛИ» 4 и «11» 3, 30 чтобы при поступлении тактового ??м ?уг?ьс??

301856

Предмет изобретения

TaemoAvu

Составитель Н. Степанов

Редактор Т. И. Морозова Техрсд А. А. Камышникова Корректор О. И. Волкова

Заказ 1916/17 Изд. М 809 Тираж 473 Подписное

Ц11ИИПИ Комитета,по делам изобретений и открытий при Совете Министров СССР

Москва, К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 списать сигнал с логической схемы запоминания.

При совпадении во времени входного и тактового импульсов запоминание входного импульса осуществляется на элементе «И» 8 и элементе «ИЛИ» 9, при этом синхронизатор ничего не выдает, так как с выхода инвертора

1 и с выхода инвертора 10 на выходной элемент «И» 2 сигналы не поступают, и синхронизированный импульс выдается устройством с приходом следующего тактового импульса.

Следует отметить, что при реализации синхронизатора на конкретных логических элементах возможен случай, когда вводить дополнительный элемент — повторитель 8 нет необходимостии.

Импульсный синхронизатор для синхронизации входных импульсов с тактовой импуль5 сной последовательностью, состоящий из трех инверторов, двух элементов «ИЛИ» и четырех элементов «И», отличающийся тем, что, с целью исключения потери информации и появления на выходе помехи, между сигнальным

10 входом синхронизатора и выходным элементом «И» включены инвертор и логическая схема запоминания, выполненная на двух элементах «ИЛИ» и одном элементе «И», логическая схема списывания, содержащая инверТ5 тор, элементы «ИЛИ» и «И», подключена к логической схеме запоминания и третьему входу выходного элемента «И».