Устройство приоритетного обращения к блоку оперативной памяти в мультивычисл ителбнойсистеме

Иллюстрации

Показать всеРеферат

r "у

11 а! бис. г,, О П И С А Н И Е 1304580

ИЗОБРЕТЕНИЯ

Союи Соеетонна

Содналнотннеонна

Реолтблнн

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт, свидетельства №

За яглено 02Х!1.1969 (№ 1341668. 18-24) МПК С 06f 9,118 с пр;1соедииением заявки №

Приоритет

Опубликовано 25.V.1971. Бюллетень ¹ 17

Комитет по делам нзобратеннд н отнрытнй орн Совете й1нннотрое

СССР

УДК 681.326.3 (088.8) Дата опубликования описан;1я 28Л 1.1971

Авторы изобретения M. А. Алексеевский, М. П. Гальперин, А. В. Иванов и И. 3. Коминаров

Заявитель

УСТРОЙСТВО ПРИОРИТЕТНОГО ОБРАЩЕНИЯ К БЛОКУ

ОПЕРАТИВНОЙ ПАМЯТИ В МУЛЬТИВЬ1ЧИСЛИТЕЛЬНОЙ

СИСТЕМЕ

Данíî= изобрсте1шс относится к области

В1>.. I BC. IB fC.7bl!OÉ ТЕХНИКИ.

Известны устройства приоритетного обраиен11я и блоку оперативной памяти в мультивычислительной системе, содержащие регистры приоритетов, регистры заявок, логические схемы, триггеры занятости.

Иедостатком известных устройств является статисти-1еское назначение приоритетов вычислителей, 1то значительно усложняет организацию решения задач в мультивычислител1и ой системе.

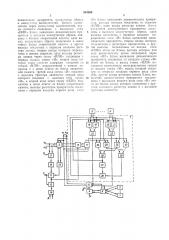

Преимуществом предложенного изобретения является обеспечение независимого многn«pbò! Iîãо обращения либого из вычислителе11 1 . б 70K Ог1еративной памяти д1нами-1еск:1х приоритетов, зависящих от приоритетов решаемь1х задач. С этой целью в устройство введены блок выявления динамиеского приоритета, коммутатор сброса и к0;I утатор вычислителей, причем вычисли1ели .срез коммутатор вычислителей, входы к0! Opofo соединены с выходами схем «ИЛИ» блока выявле:1ия динамического приор11тега и входами коммутатора сброса, связаны с блоком опсратив:1ой памяти. Один выход коммутатора сброса подключен к шине ответа

I>. 0II;: оперативной памяти, а другие выходы соедин ilbl с первыми входами регистра зая150к, вторые входы которого по:1к 710÷å! IBI к шш1ам запросов; од1ш выходы регистра заяво. через схех1у «ИЛИ» соединены с первым входом схемы «И», второй вход которой через элемент задержки соединен со схемой

5 «ИЛИ», подклю:енной к шинам запросов к шине ответа из блока оперативной памяти. третий вход с емы «И» соединен с выходом триггера занятости. Первый вход последнего ссединен с выходом этой схемы «И», а вто10 рой вход через схег, «ИЛИ» подклю неii к шина ответа из блока оперативной памяти.

Выходы регистров приоритетов соединены с первыми входами первого ряда схем «И» блока выявления динамического приоритета, 15 выходы которых соедгп1ены со схемами

«ИЛИ». Одни входы регистра заявок блока

BI,;HB7eIIIIII динамического приоритета соединены с выходом коммутатора сброса; одни выходы соединены с первыми входами пораз20 рядных схем «И» блока выявлегпия динамическоfO приоритета, вторые входы которых подкл1очены к регистрам приоритетов, а другие выхОды !103 1 7!0 IBIIb! I O BXOQBII C > B>,I «I I JI I I>> этого же блока. Выходы схем «ИЛИ» для

25 в ех вычислителей, кроме после тнего, через схе:1у «НЕ» олока выявления динами 1еского !!p:1оритета соединены со входами схемы «И» э7ого же блока, а выход схемы «ИЛИ» по0..1еднего вычислителя непосредственно связан

30 со входом > м .1 «II», вь!ход которой соеди304580 намического приоритета, коммутатор сброса и коммутатор вычислителей, причем вычислители через коммутатор вычислителей, входы которого соединены с выходами схем

«ИЛИ» блока выявления динамического при- 5 оритста и входами коммутатора сброса, связаны с блоком оперативной памяти, один выход коммутатора сброса подключен к шине ответа блока оперативной памя-.и, а другие выходь. соеди ены с первыми входами реги- 1Q стра заявок, вторые входы которого подключены к шинам запросов, одни выходы регистра заявок через схему «ИЛИ» соединены с первым в.,одом схемы «И», второй вход которой через элемент "-адержки соединен со 15 схемой «ИЛИ», подключенной и шипам запросов и к шине ответа из блока оперативной памяти, третий вход схемы «И» соединен с выходом триггера занятости, первый вход которого соединен с выходом этой схемы 20

«И», а второй вход через схему «ИЛИ» подключен к шине ответа из блока оперативной памяти, выходы регистров приоритетов соединены с первыми входами первого ряда схем

«11» блок; выявления динамического приори",;:та, выходы которых соединены со схемамц

«ИЛ11», одни входы регистра заявок блока

uü;я аления динамического приоритета, оед,iпены с выходом коммутатора сброса, одни выходы соед:гиены с первыми входами поразрядных схем «И» блока выявления динамического приоритета, вторые входы которых подклю-т ы к регистрам приоритетов, а другие выходы подключены ко входам схем

«ИЛИ» этого же блока, выходы которых для всех вычислителей, кроме последнего, через схему «1-1Е» блока выявления динамического приоритета соединены со входами схемы «И» этого же блока, а выход схемы «ИЛИ» последнего вычислителя непосредственно связан со входом схемы «И», выход которой соединен со вторымп входамп первого ряда схем

«И», другие входы регистра заявок блока выявления динамического приоритета соединенены с выходгмп второго ряда схем «И» этого же блока, входы которых соединены с другпмн выходамп регистра заявок и с вь.ходом зрпгтсра занятости.