Анализатор коротких замыканий и обрывов

Иллюстрации

Показать всеРеферат

l, О П И С А Н- -ИИЗОБРЕТЕН И

0458I Союз Советских Социалистических

Республик

Зависимое от авт. свидетельства ¹

ПК G 06f 11 00

Заявлено 13.1.1970 (№ 1394088i18-24) с присоединением заявки №

Приоритет

Опубликовано 25.Ч.1971. Бюллетень ¹

Дата опубликования описания 28ЧI.197

:Комитет по полам изобретений и открытий при Совете Министров

СССР ДК 620,179.1(088.8) Авторы изобретения

Б. С. Гомельфабр и Г. H. Кулаков

Заявитель

АНАЛИЗАТОР КОРОТКИХ ЗАМЫКАНИЙ И ОБРЫВОВ

Изобретение относится к вычислительной технике и может быть использовано на предприятиях, занима;ошихся разработкой, испытаниями и отбраковкой интегральных схем.

Известен анализатор коротких замыканий и обрывов, предназначенный для проверки кремниевых интегральных схем типа ТС-1 на отсутствие кратковременных коротких замыканий и обрывов при испытании на виброу сто йч и во сть.

Испытание интегральных схем на отсутствие кратковременных коротких замыканий и кратковременных обрывов производится в ржимах, указанных в технических условиях на испытуемые интегральные схемы.

Недостатком такого устройства обнаружения коротких замыканий и обрывов является то, что фиксирование коротких замыканий и обрывов происходит нестабильными по амплитуде перепадами напряжений, возникавшими на контактах испытуемой интегральной схемы. Возможен случай, когда при появлении короткого замыкания или обрыва амплитуда возникающего перепада будет очень мала, вследствие чего может быть нечетное срабатывание электронного реле и короткое замыкание или обрыв могут быть не зафиксированы. Если испытуемая интегральная схема заведомо имеет короткое замыкание или обрыв, то и в этом случае короткое замыкание или обрыв не будет зафиксирован. т ".åäóþùèì недостатком являются невозможность проверки на данном стенде инте5 гргльных схем милливаттной и микроваттной мошности, а также обрывов и коротких замыканий мнкросекундной длительно тн вследствие инерционности реле.

Целью предлагаемого изобретения являет10 ся создание анализатора коротких замыканий и обрывов для испытаний расширенного состава интегральных схем, фиксации обрывов и замыканий, сушествуюших в течение коротких промежутков времени (порядка десятка

15 микросекунд), повышения надежности прибора и удобства эксплуатации.

Указанная цель достигается тем, что входные контакты испытуемой интегральной схемы соединены через схемы «НЕ» с выходами

20 импульсов положительной полярности формирователя последовательностей импульсов и через схемы «НЕ» с первыми входами схем

«И» первого элемента «И вЂ” ИЛИ вЂ” HE», вторые входы которых соединены с выходами

25 импульсов отрицательной полярности формирователя последовательностей импульсов.

Выход первого элемента «И вЂ” ИЛИ вЂ” HE» через инвертор соединен со входом третьей схемы «И» второго элемента «И вЂ” ИЛИ вЂ” HE».

30 Выходы испытуемой интегральной схемы через схему «ИЛИ» соединены с первым входом первой схемы «И» и через инвертор— с первым входом второй схемы «И» второго элемента «И вЂ” ИЛИ вЂ” IE», причем вторые входы первой и второй схем «И» этого >ке элемента «И вЂ” ИЛИ вЂ” HE» соединены соответственно с выходами и!мпульсоB опроса формирователя последовательностей импульсов, выход второго элемента «И вЂ” ИЛИ вЂ” HE» соединен со входом установки нуля триггера индикации. Прп этом на входы испытуемой схемы подаются импульсы отрицательной полярности, разнесенные во времени, и анализируется прохождение этих импульсов в испытуемой интегральной схеме. В случае короткого замыкания или обрыва в контактных соединениях испытуемой интегральной схемы на выходе анализатора появляется импульс напряжения, который поступает на триггер индикации. TpHff ep сработает и загopHTch лампочка индикации.

Испытаниям могут подвергаться иптегральпые схемы, сопрягаемые по уровням логических «0» и «1» с интегральными схемами типа «Логика» и реализу!Ощие логические функции «И», «И — НЕ», «И — ИЛИ вЂ” IE».

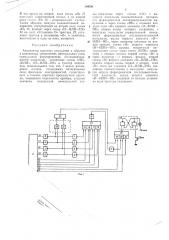

На фиг. 1 изображена блок-схема предла гаемого анализатора; на фиг. 2 — временные дп а гр а м мы.

На фиг. 1 изображены: 1 — испытуемая HEIтегральная схема; 2 — формирователь последовательностей импульсов положительной полярности и двух последовательностей импульсов опроса положительной полярности; 8—

12 — логические схемы «НЕ»; 13 — 21 — логические схемы «И»; 22 — логическая схема

«ИЛИ»; 28 — 24 — логические схемы — элементы «И — ИЛИ вЂ” HE»; 25 — триггер индикации; 26 — 29 — выходы импульсов положительной полярности формирователя последовательностей импульсов; 30 — 88 — выходы импульсов отрицательной полярности формирователя последовательностей импульсов; 84—

85 — выходы импульсов опроса формирователя последовательностей импульсов.

Испытуемой схемой 1 в данном случае является интегральная схема, в корпусе которой содержится два инвертора со схемами

«И» 18 и 14 на входе, т. е. имеется четыре входа и два выхода. Формирователь импульсов 2 формирует следующие сигналы: а) четыре последовательности импульсов положительной полярности (см. фпг. 2, а — г) — выходы 26 — 29 формирователя последовательностей импульсов; б) четыре последовательности импульсов отрицательной полярности (см. фиг. 2, д— и) — выходы 80 — 33 формирователя последовательностей импульсов; в) две последовательности импульсов опроса положительной полярности (см. фиг. 2, к — л) — выходы Я и 85 формирователя 2.

Импульсы положительной полярности с выходов 26 — 29 формирователя импульсов 2 поступают соответственно на входы логичссННх схем — 1!1!!!срторов 3 — 6. С выxолов этиx

IIIIIIepторов импульсы отрицательной полярIIOCT!I ПОСТ \ IIBIOT СООТПСТСтвСellIIO II B входи! IIC пытуемои интегральной схемы 1. С выходов последней импульсы положительной полярности поступают liB входы схемы «ИЛИ» 22, с выхода которой 1!мпульсное напряжение типа меандр (см. фиг. 2, я1) подается па вход схемы «И» 19. Это импульсное напряжение

)Q является запрещающим сигналом для импульсов положительной полярности (фиг. 2, л), поступающ!!х с выхода 3 1 формирователя импульсов па второй вход с. емы «И» 19.

Импульсное напряжение с выхода схемы

«ИЛИ» 22 поступает также па вход инвертора 11, с выхода которого импульсное напряEIicilHc пост > HBcT II;! Первый BxoE cxP.; 11>l «И»

20. iTO импульсное напряжение является Вапрещающим сигналом для импульсов положительной полярности (см. фи!. 2, к), поступающих с II. :Ixo EB 35 формирователя импульсов 2 на второй вход схемы «И» 20.

Если в исш1тусмой схеме будет обрыв хотя бы одной входной цепи или в цщ1п питапи>1, или короткое замыкание в цепи питания, то одно из импульсных папря>ке!!ий, поступающих на первые входы схем «И» 19 и 20, в моменты обрыва и короткого замыкания будут разрешающим сигналом для импульсов положительной полярности. Эти импульсы пройдут через схему «И — ИЛИ вЂ” НВ» 24 на вход «Установки «О» трипера 25 и установят триггер в поло>кение «О». Лампочка, включенная в одно из плеч, загорится.

OoHapyE«el!He коротких замыканий во входных цепях испытуемой интегральной схемы происходит следующим образом.

Входы испытуемой интегрально!1 схе,lbl

cоОтве fcTHcEIEIo соединены со входамп ппьср4р торов 7 — !О. 1 11ким Ооразом) имп>льсы Отрицательной полярности, поступающие па входы испытуемой интегральнои схем,l, пост> -" па!от и на входы и 7 — 10, с B! Ixoдов которых EIмпульсы положительной поляр45 ности поступают на первые входы схем «И»

15, 16, 17» 18.

Ha;е входы этих схем поступают соответственно импульсы отрицательной полярности (см. фиг. 2, д — и) с выходов 30 — 33 формирователя импульсов 2, которые явля!отся запре1ца:ощими сигналами для соответствующих импульсов положительной полярности, поступающих па первые входы схем «И»

15, 16, 17 и 18. В случае, если имеется короткое замыкание во входных цепях испытуемой схемы, например первьш контакт испытуемой интегральной схемы l.имеет короткое замыкание со вторым контактом, тогда импульс отрицательной полярности, поступающий на первый контакт испытуемой интегральной схемы, пройдет IIB вход ипвертора 7 и по цепи короткого замыкания IIB вход инвертора

8. С выходов инверторов 7 и 8 импульсы положительной полярности поступят соответст65 веппо па первые входы схем «И» 15 и 16.

504581

В это врс!!я»а второй вход схемы «И» 15 поступает запрещающий сигнал, а иа второй вход схемы «И» 16 — разрешак>щий с!!гнал.

Таким образом, импульс положительной полярности, поступающий на второй вход схемы

«И» 16, пройдет через схему «И — ИЛИ вЂ” НЕ»

24 на вход «Установка О» триггера 25, установит триггер в положение «0», и лампочка, включенная в одно из плеч, загорится.

Предмет изобретения

Анализатор коротких замыканий и обрь:вов в контактных соединениях интегральных схем, содержащ:!й формирователь последовательностей импульсов, логические схемы «НЕ», «ИЛИ», «И — ИЛИ вЂ” HE» и триггер индикации, отличаюш,ийся тем, что, с целью расширения состава испытуемых интегральных схем, фиксации неисправностей, существующих в течение коротких промежутков времени, повышения наде>к»ости прибора, входные контакты испытуемой интегральной схемы соединены через схемы «НЕ» с выходами импульсов положительной полярностl! формирователя последовательностей импульсов и через схемы «НЕ» с первыми вхо5 дами схем «И» первого элемента «И вЂ” ИЛИ—

НЕ», вторые входы которых соединены с выходами импульсов отрицательной полярности формирователя последовательностей импульсов, выход первого элемента «И—

lo ИЛИ вЂ” HE», через инвертор соединен со входом третьей схемы «И» второго элемента

«И — ИЛИ вЂ” HE», выходы испыт емoi интеграль»ой схемы через схему «ИЛИ» соеди»ены с перзым входом первой схемы «И» и

1 через иивертор — с первым входом второй схемы «И» второго элемента «И вЂ” ИЛИ вЂ” HE», причем вторые входы первой и второй схем

«Н» этого же элемента «И вЂ” ИЛИ вЂ” HE» соединены соотвстствепно с выходами импуль20 сов опроса формирователя последовательностей импульсов, выход второго элемента

«И — ИЛИ вЂ” НЕ» соединен со входом установки и > ля Tp»I Ãñpа и»дикации.

304581

Составитель В. А. Кудрявцев

Редактор Б. С. Нинкина Техред А. А. Камышникова Корректор Т. А. Китаева

Заказ 1747j 17 Изд. № 725 Тираж 473 По

ЦНИИПИ Комитета по делам изобретений ti открытий при Совете Мин "

Москва, %-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, ?