Патент ссср 305587

Иллюстрации

Показать всеРеферат

О П И СА Н И Е

ИЗОБРЕТЕНИЯ

305587 бова Соеетскик

Социалистические

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

МПК Н 03k 19/00

Заявлено 25.XI I.1969 (№ 1389146/18-24) с присоединением заявки №

Приоритет

Опубликовано 04.Ч1.1971. Бюллетень Х 18

Дата опубликования описашгя 23.Ч11.1971

Комитет по делам изобретений и открытий ори Совете Министров

СССР

УДК 621.374.32(088.8) Автор изобретения

С. А. Бирюков

Заявитель

ИНВЕРТОР

Изобретение относится к области вычислительной техники, в частности к инверторам, построенным на интегр альных схемах.

Известны инверторы, содержащие входной многоэмиттерный транзистор, выходной инвертирующий транзистор, выходной эмиттерный повторитель и промежуточный каскад, выполненный на двухэмиттерном транзисторе, два эмиттера которого подключены к базе и к коллектору выходного инвертирующего транзистора.

Однако такие инверторы имеют низкую помехоустойчивость и недостаточно высокое быстродействие.

Целью изобретения является создание инвертора с более высокой помехоустойчивостью и ббльшим быстродействием. Для этого в схему инвертора дополнительно введены транзистор и несколько диодов.

Такое построение инвертора позволило создать более быстродействующие интегральные схемы с повышенной помехоустойчивостью к емкостиым помехам.

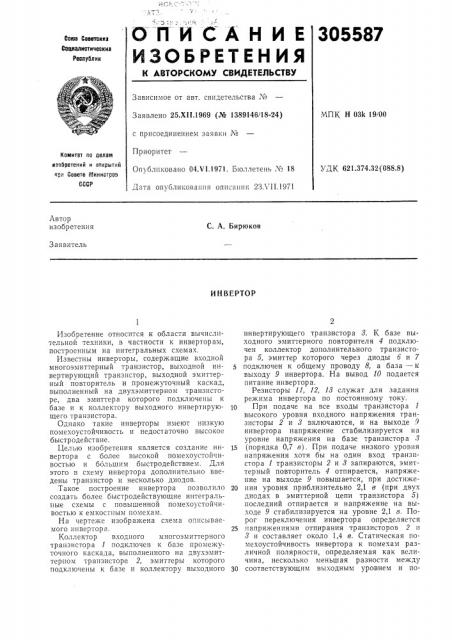

На черте>ке изобра>кена схема описываемого инвертора.

Коллектор входного многоэмиттерного транзистора 1 подключен к базе промежуточного каскада, выполненного на двухэмиттерном транзисторе 2, эмиттеры которого подключены к базе и коллектору выходного инвертирующего транзистора 8. К базе выходного эмиттерного повторителя 4 подключен коллектор дополнительного транзистора 5, эмиттер которого через диоды 6 и 7 подключен к общему проводу 8, а база — к выходу 9 инвертора. На вывод 10 подается питание инвертора.

Резисторы 11, 12, 18 служат для задания режима инвертора по постоянному току.

10 При подаче на все входы транзистора 1 высокого уровня входного напряжения транзисторы 2 и 8 включаются, и на выходе 9 инвертора напряжение стабилизируется на уровне напряжения на базе транзистора 8

15 (порядка 0,7 в). При подаче низкого уровня напряжения хотя бы на один вход транзистора 1 транзисторы 2 и 8 запираются, эмиттерный повторитель 4 отпирается, напряжение на выходе 9 повышается, при достиже20 нии уровня приблизительно 2,1 в (при двух диодах в эмиттерной цепи транзистора 5) последний отпирается и напряжение на выходе 9 стабилизируется на уровне 2,1 в. Порог переключения инвертора определяется

25 папряжениями отпирания транзисторов 2 и

8исоставляет около 1,,4 в. Статическая помехоустойчивость инвертора к помехам различной полярности, определяемая как величина, несколько меньшая разности между

30 соответствующим выходным уровнем и по305587

Предмет изобретения

05в 0

2,1s — 0,7в

Составитель Л. А. Пронин

Текред T. H. Курилко Корректор О. С. Зайц-në

Редактор Загребельная

Заказ 1967/17 Изд. ¹ 852 Тираж 473 Подписное

ЦНИИПИ Кок1нтета по делана изобретений и открытий при Совете М|шнстров СССР

Москва, 7К-35, Раугиская наб., д, - !!5

Тппогра<рия, пр. Сапунова, 2 рогом переключения, составляет для помех обеих полярностей величину около 0,5 в, т. е. такую >ке, как и помехоустойчивость известных инверторов к помехам положительной полярности. Устойчивость к помехам, вызываемым емкостной связью проводников, пропорциональна отношению статической гомехоустойчивости к полному перепаду напряжения на выходе инвертора и составляет для описываемой схемы величину

Повышение быстродействия описываемой схемы обусловлено тем, что крутизна фронтов сохраняется, а амплитуда выходного перепада и, следовательно, длительность фронтов уменьшается.

Оптимальное число диодов в эмиттерной цепи дополнительного транзистора два, однако инвертор может работать и с ббльшим

ЧИСЛОМ ДИОДОВ.

Инвертор, содержащий выходной ппвертирующий транзистор, выходной эмиттерный

5 повторитель, входной двухэмиттерпый инвертирующий транзистор, один из эмиттеров которого подключен к базе, другой — к коллектору выходного ипвертирующего транзистора, база подключена ко входу инвертора

10 через входную логическую схему, выполненную, например, на многоэмиттерном транзисторе, причем коллектор выходного инвертирующего транзистора и эмнттер транзистора выходного эмиттерного повторителя подклю15 чены к выходу инвертора, коллектор входного инвертирующего транзистора подключен к базе транзистора выходного эмигт рпого повторителя, отлика, ощийся тем, -гго, с целью увеличения помехоустойчивости и быстро20 действия, в схему и",âåðòîðà введен дополнительный транзистор, коллектор которого подключен к базе транзистора выходного эмиттерного повторителя, база — - к выходу инвертора, эмиттер — к общему проводу через

25 последовательно соединенные диоды.