Аналого-цифровой преобразователь;. ," --хк1'?1н?ш!

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

306563

Сова Советскив

Социалнстическик

Республик

Зависимое от авт. свидетельства №вЂ”

Заявлено 27.XI.1969 (_#_8 1379853/18-24) с присоединением заявки №вЂ”

Приоритет—

Опубликовано II.VI,1971. Бюллетень № 19

Дата опубликования описания 5 VI I 1.1971

МПК Н 03k 13/20

Н 03k 13/17

Номитет по делам изобретений н открытий при Совете Министров

СССР

УДК 681.325(088.8) Авторы изобретения

В. П, Сафронов, К. В. Сафронова, А. Г. Рыжевский, М. П. Шадрин и В. М. Шляндин

Пензенский политехнический институт

Заявитель

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЪ

Изобретение относится к области вычислительной техники и автоматики

Известны аналого-цифровые преобразователи (АЦП), содержащие дифференциальный усилитель, блок по|роговых элементов, регистр состояний пороговых устройств, сумматор, преобразователь код — аналог, блок управления. В таких преобразователях величина ступени компенсирующего напряжения пропорциональна при ращению преобразуемого нацряжения за время такта. Выбор значений порогов срабатывания пороговых элементов и их количество определяет как допустимую скорость U, изменения, так и динамическую погрешность.

Все известные АЦП накладывают ограни:ения на скорость изменения входного сигнала, которые вызваны тем. что компенсация вводится с учетом величины разбаланса в момент опроса, Увеличение скорости U „ïðèâîäèò к существенному увеличению величины разбаланса в момент опроса. Поэтому для уменьшения динамической погрешности необходимо значительно увеличить число, пороговых элементов.

Целью изобретения является уменьшение динамической погрешности (увеличение динамической точности) следящих АЦП путем ведения процесса компенсации с учетом ско рости изменения входной величины без увеличения числа пороговых элементов и при сохранении такта преобразования.

Эта задача .решается с помощью двойного опроса состояний пороговых элементов с

5 заданным интервалом времени, выделения кода дифференциала входного сигнала и соответствующих логических операций, приводящих к тому, что величина ступеней компенсирующего напряжения выдается с таким расчетом, чтобы величина разбаланса в момент опроса была минимально возможной и не накапливалась за время такта. К роме гого, перед выдачей результата преобразования осуществляется коррекция динамической по15 греш ности. ,Предложенное устройство отличается от известных тем, что содержит дополнительный, регистр, вычитатель кодов и клапаны, причем входы основного и дополнительного регистров

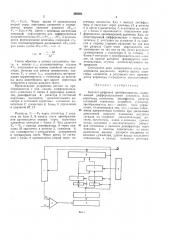

20 соединены с выходом дешифратора через клапаны, а,выходы — подключены ко входу вычитателя, выходы кото рого соединены со входами сумматора. Другие входы сумматора подключены к выходу основного регистра, 25 На фиг. 1 изображена структурная схема устройства; на фиг. 2 — временная диатрамма такта преобразования.

В начале такта (момент t;) производится опрос состояний пороговых элеменгов и опреЗО деляется первое значение разности

306563

e. — — М где т

Фиг t (V, — V ) 1;. Чврез время 4t производится второй опрос пороговых элементов и определяется второе значение разности 4V„. =

V, — V>(t;+ t). Затем с помощью логических операций определяется код дифференциала входной величины Л -=4 V,, — V,, и производится формирование величины очередной ступени компенсирующего напряжения Vq, которая равна сумме V<= V,., +m . Л, Таким образом, к началу следующего такта в момент t,+> устанавливается ступень

Л V,, полученная на основе линейной экстраполяции, близкая или равная мгновенному значению V,. в точке t,+, погрешность экстраполяции корректируется с точностью до величины шага квантования, при опросе пороговых элементов в начале каждого такта.

Предлагаемое устройство состоит из преобразователя 1 код — аналог, дифференциального усилителя 2, блока 8 пороговых элементов, дешиф ратора 4, регистра 5 состояний пороговых элементов, дополнительного регистра б состояний пороговых элементов, вычитателя 7, сумматора 8, блока 9 управления и клапан,ов 10, 11.

Разность V,, — Vn через усилитель 2 подается на блок 8. В начале такта преобразова ния производится первый опрос пороговых элементов сигналом с блока 9. Код разности

V„— V с выхода деши фратора 4 через кла,паны 10 заносится в регистр 5, сумматор 8, где сумми руется с результатом кодирования в предыдущем такте. Через время t сигналом с блока 9 производится второй опрос пороговых элементов. Код с выхода дешифратора 4 поступает через клапаны li в регистр б и затем в вычитатель 7, в котором по сигналу с блока 9 производится определение диф5 фе ренциала преобразуемой величины, Код, соответствующий дифференциалу с выхода вычитателя 7, поступает на сумматор 8 со сдвигом в сторону старших разрядов на два или три,разряда, Сдвиг кода эквивалентен его умножению на «4» или на «8». Затем результат суммирования с сумматора 8 по сигналу с блока 9 поступает в преобразователь кад — аналог, на выходе которого формируется соответствующая ступень компенсирующего наг ря|ж ен и я.

Считывание кода производится после суммирования результата первого опроса пороговых элементов, в результате чего производится коррекция погрешности экстраполяции.

Предмет изобретения

Аналого-цифровой преобразователь, содер25 жащий дифференциальный усилитель, блок пороговых элементов, дешифратор, регистр состояний пороговых устройств, сумматор, преобразователь код — аналог, блок управления, отличающийся тем, что, с целью сохразО нения дннамичеокой точности при увеличен ни допустимой скорости изменения входного сигнала, он содержит дополнительный регистр, вычитатель кодов и клапаны, причем входы основного и дополнительного регистЗ5 ров соединены с выходом дешифратора через клапаны, а выходы подключены ко входу вычитателя, выходы которого соединены со входами сумматора, другие входы последнего подключены к выходу основного регистра.

306563

Фце 2

Составитель В. Д. Махнаков

Редактор В. С. Левитов Техред А. А. Камышникова Корректор О. И. Волкова

Заказ 281/1062 Изд. Х 783 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, К-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред, «Патент»