Патент ссср 306567

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №вЂ”

Заявлено 30.1!1.1970 (№ 1420429118-24) с присоединением заявки ¹â€”

Приоритет—

Опубликовано 11.V 1.1971. Бюллетень ¹ 19

Дата опубликования описания 5Л 111.1971.ЧПК Н 03k 19, 24

Комитет по делам изобретений и открытий при Совете Министров

СССР

УД К 681.3.325 (088.8) Автор изобретения

М. К. Скучас

Заявитель

СХЕМА СОВПАДЕНИЯ

Изобретение относится к области вычислительной техники и автоматики и может быть применено для ввода и нормализации кодовых значений от различных измерительных приборов, имеющих кодовые выходы, в устройства обработки данных.

Известны схемы совпадения, на один вход которых подаются подлежащие обработке сигналы с измерительного прибора, а на другой — уровень постоянного тока, соответствующий логической единице на выходе измерительного прибора. В этом случае на выходе схемы совпадения получается сигнал, кодовые уровни которого имеют заранее установленную величину и поэтому могут проходить дальнейшую обработку.

Однако известные схемы могут быть применены только в случае, если в момснт совпадения амплитуды сигналов на входах равны, т. е, при идентичных подаваемых уровнях сигналов. Кроме того, эта схема имеет сравнительно низкое быстродействие из-за влияния паразитной емкости между базой и эмиттером транзисторов, Цель изобретения — создание быстродействующей схемы совпадения с определенной зоной допустимого неравенства входных сигналов в момент совпадения.

В предложенной схеме для повышения быстродействия применяются ускоряющие конденсаторы. шу тирующие базовые резисторы, а для установления определенных пределов допустимых изменений уровня входных сигналов используются стабилизирующие диоды в цепях без транзисторов.

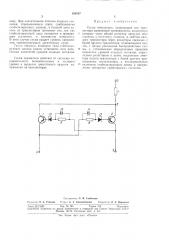

Схема совпадения показана на чертеже.

Она содержит два транзистора 1, 2 одного типа проводимости, соединенных коллекторами в точке 8, к которой подается напряженпс питания через резистор 4 от клеммы 5. Эмиттеры транзисторов 1 и 2 выводятся на клеммы

6 Ii 7, 1 0TopbIe BBляются входными клеммами схемы совпадения. Эмиттер транзистора I через резистор 8 соединен с базой транзистора

2, а эмиттер транзистора 2 через резистор 9— с базой транзистора 1.

Для увеличения быстродействия базовые резисторы 8 и 9 шунтируются ускоряющими конденсаторами 10 и 11, а для достижения определенной зоны изменения уровней входных сигналов в базовые цепи транзисторов включены стабилизирующие диоды 12 и 18.

Входные уровни сигналов на клеммах 6 и

7 в момент совпадения могут отличаться на определенную величину. Максимальная величина этого отличия равна порогу срабатывания диодов 12 и И. Прп неравенстве входных сигналов, не превышающем эту максимальную величину, схема в точке 3 выдает уровень напряжения, соответствующий логической едп306567

Предмет изобретения

Составитель Л. В. Скобелева

Реда«тор Л. А. Утехина Техрод А. А. Камышникова Корректор Л. А. Царькова

3 а к а з 28 I, 10б2 Изд. № 783 Тираж 473 Подписное

ЦКИИПИ Комитета по делам изобретений и открытий прп Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент> нице. При значительном отличии входных сигналов, (превышающем порог срабатывания стабилизирующих диодов), в базовой цепи одного из транзисторов протекает ток, так как стабилизирующий диод находится в проводящем состоянии, и транзистор отпирается.

В этом случае схема выдает уровень напряжения, соответствующий логическому нулю.

Таким образом, подбором типа стабилизируюгцих диодов можно установить зону допустимых изменений уровней входных сигналов.

Схема нормально работает от сигналов отрицательного, положительного и нулевого уровня в пределах допустимого падения напряжения на транзисторах.

Схема совпадения, содержашая два транзистора одинаковой проводимости, коллекторы

5 которых через общий резистор нагрузки подключены к источнику питания, а эмиттер каждого транзистора через резисторы соединен с базой другого транзистора, отличающаяся тем, что, с целью увеличения быстродействия схе10 мы и установления определенных пределов изменения уровней входных сигналов, параллельно резисторам в цепях соединения эмиттера одного транзистора с базой другого присоединены конденсаторы, а последовательно включены стабилизирующие диоды в направлении запирания сравниваемых сигналов.