Преобразователь двоично-десятичного кода в двоичный и обратно

Иллюстрации

Показать всеРеферат

ЗО8426

ОПИСАНИЕ

ИЗОЫЕт ЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

6оюз Соеетския

6оциалистических

Республик

Зависимое от авт, свидетельства ¹

Заявлено 19.111.1969 (№ 1312905/18-24) с присоединением заявки №

Приоритет

Опубликовано 01.Ч11.1971. Бюллетень № 21

Дата опубликования описания 12.VIII.1971

ЧПК G 06f 5/02

Комитет по делам

Изобретеиий и открытий при Совете Министров

СССР

УДК 681.325.53 (088.8) Авторы изобретения

Б. А. Пряхин и О. Д. Жуков-Емельянов

Заявитель Научно-исследовательский центр электронной вычислительной техники

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА

В ДВОИЧНЫЙ И ОБРАТНО

Изобретение относится к области автоматики и вычислительной техники и предназначено для преобразования кодов.

Известны преобразователи двоично-десятичного кода в двоичный и двоичного кода в двоично-десятичный, выполняющие преобразование с помощью комбинационных схем соединений между разрядами входного регистра и соответствующими разрядами су мматора.

Предложенное устройство отличается тем, что при преобразовании (n+1) -разрядного десятичного числа, выход каждого разряда сумматора, кроме (4n+1)-го, соединен со входом соответствующего разряда первого регистра, выход 1-то разряда первого регистра (i 1, 2, ..., 4(n+1)) соединен со входом (4(п — I)+i)-ro разряда второго регистра, выход 1-го разряда второго регистра (1=5, 6, ..., 4n, (8п+4), ..., 12п) соединен по цепи сдвига со входом (1 — 4) -го разряда того же регистра, выход

k-го разряда второго регистра (k= (4n+I), ..., ..., 8п), кроме (Sn — 2) -го разряда, соединен с первым входом m-ro разряда сумматора (т=

=4, 5, ..., (4и+3), и, кроме 8n-ro разряда, соединен со вторым входом q-го разряда сумматора (q=2, 3, ..., 4п), а выходы (8п+2), (8п+3) и (8n+4)-го разрядов второго регистра соединены со вторыми входами (4n+2), (4n+3) и (4n+4)-го разрядов сумматора соответственно, причем выходы (8п+2) и (8n+

+1)-го разрядов того же регистра соединены через первую схему «ИЛИ» с первым входом (4n+1) -го разряда сумматора, а также соединены со входами первой схемы «И», соединенной по входу также с выходом 8n ro разряда второго регистра, а выход этой схемы «И» и выход (4п+1)-го разряда сумматора соединены через вторую схему «ИЛИ» со входом

10 (4и+1)-го разряда первого регистра, причем выходы (8n — 2) и (8п — 1) -ro и инверсный выход 8п-ro разрядов второго регистра соединены со входами второй схемы «И», а выход этой схемы «И» и выход 8п-го разряда второ15 го регистра соединены через третью схему

«ИЛИ» со вторым входом (4п+1)-го разряда сумматора.

Это позволяет повысить быстродействие устройства и упростить его схему за счет выпол20 нения в каждом разряде одновременного сложения трех слагаемых на двухвходовом сумматоре.

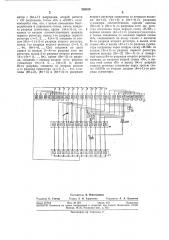

Схема устройства для и-2 изображена на чертеже. Устройство содержит 12-разрядный

2s первый регистр 1, выполненный на триггерах

2 — 18, сумматор 14, выполненный на двенадцати одноразрядных сумматорах 15 — 2б, 24— разрядный второй регистр 27, выполненный на триггерах 28 — 51, схемы «ИЛИ» 52, 58 и 54, ЗО схемы «И» 55 и 5б.

308426 составитель В. Игнатущеико

Техред 3, Н. Тараиеико Корректор Л. А. Царькова

Редактор Е. Гончар

Заказ 2176/4 Изд. № 951 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

5 матор с (4п+1) разрядами, второй регистр с 12п разрядами, схемы «И» и «ИЛИ», отликаюи ийся тем, что, с целью повышения быстродействия и упрощения схемы, выход каждого разряда сумматора, кроме (4n+1)-го, соединен со входом соответствующего разряда первого регистра, выход i-го разряда первого регистра (1= 1, 2, ..., 4(п+1) соединен со входом (4(n — 1)+1)-го разряда второго регистра, выход 1-го разряда второго регистра (1=5, 6, ..., 4n; (8п+4), ..., 12п) соединен по цепи сдвига со входом (1 — 4) -го разряда того же регистра, выход k-го разряда второго регистра (k= (4n+1),, 8п), кроме (8п — 2)-ro разряда, соединен с первым входом т-го разряда сумматора (m=4, 5, ..., (4п+3) и, кроме

8n-ro разряда, соединен со вторым входом

q-го разряда сумматора (q=2, 3, ..., 4п), а выходы (8п+2), (8п+3) и (8n+4)-го разрядов второго регистра соединены со вторыми входам и (4n+ 2), (4п+ 3) и (4п+ 4) -го р азрядов сумматора соответственно, причем выходы (8п+2) и (8п+1)-го разрядов того же реги5 стра соединены через первую схему «ИЛИ» с первым входом (4n+1) -го разряда сумматора, а также соединены со входами первой схемы

«И», соединенной по входу также с выходом

8п.-го разряда второго регистра, а выход этой

10 схемы «И» и выход (4n+1)-го разряда сумматора соединены через вторую схему «ИЛИ» со входом (4n+1) -го разряда первого регистра, причем выходы (8n — 2) (8n — 1)-го и инверсный выход 8п-го разрядов второго регистра со)5 единены со входами второй схемы «И», а выход этой схемы «И» и выход 8п-го разряда второго регистра соединены через третью схему «ИЛИ» со вторым входом (4n+1)-го разряда сумматора.