Устройство для умножения частоты следования импульсов на переменные коэффициенты

Иллюстрации

Показать всеРеферат

О rI И С А Н И Е 308523

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Севе Соеетоких

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 10.XII.1969 (№ 1384124/18-24) МПК H 03k 23/00

Ci 06f 7/52 с присоединением заявки ¹

Приоритет

Опубликовано 01.V11.1971. Бюллетень № 21

Дата опубликования описания 23.VI II.1971

Комитет по делам изобретений и открытий при Соаете Министров

СССР

УДК 621.374.44.681. .325.5 (088.8) Авторы изобретения

Л. С. Зеленов и В. И. Колосков

Заявитель

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ НА ПЕРЕМЕННЫЕ КОЭФФИЦИЕНТЬ1

Изобретение относится к области автоматики и может быть использовано в частотно-импульсных вычислительных и моделирующих устройствах.

Известны устройства умножения частоты следования импульсов на коэффициенты, в которых используется делитель частоты на статических триггерах, коммутаторы и импульсные схемы «ИЛИ».

Однако такие умножители имеют большое число коммутаторов, а коэффициенты умножения не могут быть больше единицы.

Целью изобретения является получение возможности умножения частоты на коэффициенты больше единицы и уменьшение числа коммутаторов для случая, когда все коэффипиенты умножения требуется изменять в одинаковое число раз, f Ê,=f К К,=F К, f К2 f К К2 F К2

f.Ki f K.K F Ki

f К =f К.К =F.Ê где f — входная частота;

К; — коэффициент умножения;

F — частота на входе делителя частоты;

К вЂ” переменный коэффициент, К» К К;... К вЂ” постоянные коэффициенты, Предлагаемое устройство умножения, с целью

ego упрощения, содержит цепь импульсной обратной связи, состоящую нз сумматора и элемента задержки, вход элемента задержки соединен с выходом схемы «ИЛИ», а выход через сумматор подключен к входу делителя частоты.

Частота импульсных последовательностей тех или иных разрядов делителя частоты скла1р дываются с входной частотой устройства умножения или вычитаются из нее, после чего вновь поступают на вход делителя частоты.

Изменение модуля коэффициента обратной связи, осуществляемое с помощью коммута15 торов в цепи обратной связи, приводит к одновременному изменению всех коэффициентов умножения. В случае положительной обратной связи коэффициенты умножения могут быть больше единицы.

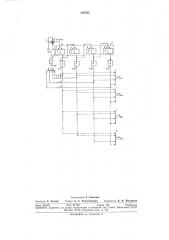

На чертеже изображена функциональная схема предлагаемого устройства умножения.

Предлагаемое устройство умножения содержит делитель частоты 1 íà и статических триггерах 2, т импульсных схем «ИЛИ» 8, которые подключены своими входами в зависимости от значений коэффициентов F„Кз ..., К;... К к тем пли иным разрядам делителя частоты через дифференцирующие цепи 4. Кроме того, в устройство умножения

3р входят частотно-нмпульс ый сумматор 5, ком308523 мутатор знака обратной связи 6, элемент задержки 7, импульсная схема «ИЛИ» 8 цепи обратной связи, которая с помощью и коммутаторов 9 подключается своими входами, в зависимости от значения коэффициента Й, к тем или иным разрядам делителя частоты через дефференцирующие цепи.

Входные импульсы с частотой повторения f проходят через частотно-импульсный сумматор и поступают на первый триггер делителя частоты. Положительные перепады напряжения триггеров делителя являются сигналом переноса «I» в следующий разряд делителя частоты.

Из отрицательных перепадов триггеров делителя частоты с помощью дифференцирующих цепей формируются импульсы, частота повторения которых равна .2 — 1 г.2 — 2 г.2 — 1 т .2 — л где Р— частота на входе делителя частоты;

i — номер разряда делителя частоты.

Импульсы на выходах дифференцирующих цепей никогда не совпадают по времени. Умножение частоты F на постоянные коэффициенты К„К ..., К,,..., К производится соответственно на схемах «ИЛИ» 8 путем подключения входов схем «ИЛИ» к дифференцирующим цепям тех разрядов делителя частоты, в которых данный коэффициент, представленный в двоичном коде, имеет 1, F K> — a> F 2 — +а F 2- +...+

+a> F 2 — +...+а F 2-", где а;, равно О или 1.

На функциональной схеме цепи соединения входов импульсных схем «ИЛИ» с дифференцирующими цепями делителя частоты показаны пунктиром.

Умножение частоты F на коэффициент обратной связи К осуществляется путем подключения с помощью коммутаторов 9 входов импульсной схемы «ИЛИ» 8 к дифферспцирующим цепям тех разрядов делителя частоты, в которых коэффициент К, представленный в двоичном коде, имеет 1:

F К =в, F.2 — +в,.F 2 — +. +

+ в1 F 2 +... +вп F-2-и где

b; равно О или 1.

С выхода схемы «ИЛИ» 8 импульсы с частотой повторения F К задерживаются на элементе задержки 7. Задержка импульсов обеспечивает разделение во времени импульсов, поступающих на частотно-импульсный сумматор 5 по разным входам, что позволяет производить алгебраическое сложение частот практически без погрешностей

f+F К =F

ТаккакF=f К,то f+f КК =f К.

Из последнего уравнения получаем выражение для определения значения коэффициента обратной связи К, при котором обеспечивается требуемое значение коэффициента К

К =1

К

Модуль коэффицента обратной связи К может принимать дискретные значения в пределах от О до (1 — 2 — ") с шагом 2 — ". Знак коэф15 фициента обратной связи может быть положительным и отрицательным. Реализация знака коэффициента обратной связи К осуществляется путем переключения с помощью коммутатора б частотно-импульсного сумматора 5

20 либо на суммирование входной частоты f и частоты F К (К ) 0 — положительная обратная связь»), либо на вычитание из входной частоты f частоты F К I (< (О— отрицательная обратная связь»). При положы25 тельной обратной связи коэффициент умножения.

К=

К1

30 а диапазон изменения К лежит в пределах от

1 (при К = О) до значений К ) 1, определяемых быстродействием элементов устройства умножения (при 1 (К1 (О). При отрицательной обратной связи коэффициент К =

35 1, а диапазон изменения К лежит

1 + (К ) в пределах от 0,5 (при К = 1) до 1 (при

К = О).

40 Таким образом, предлагаемое устройство умножения позволяет при числе коммутаторов равном и + 1 одновременно изменять коэффициенты умножения %, К2,... К;,... К в сторону уменьшения на 50% и в сторону

45 увеличения до значений, определяемых быстродействием элементов устройства умножения.

Предмет изобретения

Устройство для умножения частоты следования импульсов на переменные коэффициенты, содержащее делитель частоты, коммутаторы и схемы «ИЛИ», причем выходы разрядов де55 лителя ча стоты через коммутаторы соединены со входами схем «ИЛИ», отличающееся тем, что, с целью упрощения устройства, оно содержит цепь импульсной обратной связи, состоящую из сумматора и элемента задержки, gp вход элемента задержки соединен с выходом схемы «ИЛИ», а выход через сумматор подключен ко входу делителя частоты.

308523 г — -э

Составитель Е. Семенова

Редактор Е. Гончар Тсхред А. А. Камышникова Коррсктор В. И. )Колудева

Заказ 2218/5 Изд, № 967 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Я-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

1