Приемник составных сигналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

3ll409

Союз Соеетскик

Социалистическиз

Республик

К АВТОРСИОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 03.11.1970 (№ 1401993/26-9) с присоединением заявки №

Приоритет

Опубликовано 09 VIll.1971. Бюллетень № 24

Дата опубликования описания 6.Х.1971

МПК Н 04Ь 1/10

Комитет по делам изобретений и открытий лри Совете Министров

СССР

УДК 621.394.4(088.8) Авторы изобретения

Н. Б. Резвецов и М. Г. Вяткин

Заявитель

ПРИЕМНИК СОСТАВНЪ|Х СИГНАЛОВ

Предлагаемое устройство относится к области передачи сигналов и может быть использовано в системах передачи дискретных данных по каналам радиосвязи при приеме составных сигналов, образуемых постоянным числом элементов, выбранных из биортогонального ансамбля.

Известны приемники составных сигналов, образуемых постоянным числом элементов, содержащие фильтр, согласованный с элемен- 10 тами составного сигнала, инверторы, решающий блок, преобразователь кодов и хронизатор.

Целью изобретения является увеличение возможного числа опознаваемых сигналов, по- 15 вышение точности опознания и быстродействия системы передачи дискретных данных при одновременном упрощении схемного решения.

Это достигается тем, что между выходами согласованных фильтров и инверторов и вхо- 20 дами указанного блока дополнительно включены диодно-резисторные коммутирующие схемы, а к выходам решающего блока подключен набор триггеров, причем потенциальный выход каждого триггера соединен с дио- 2s дом коммутирующей схемы, а импульсный выход триггера соединен с преобразователем кодов.

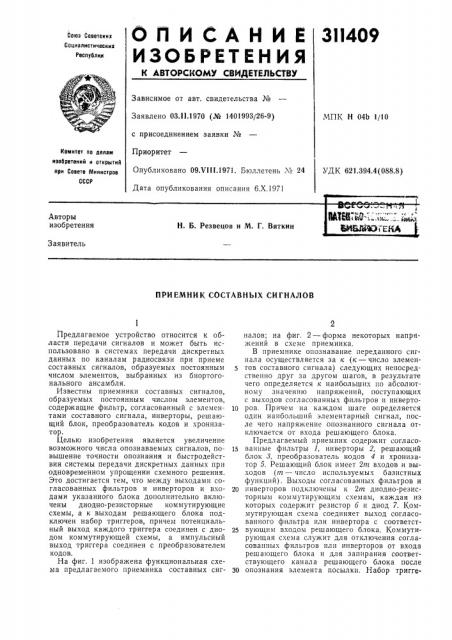

На фиг. 1 изображена функциональная схема предлагаемого приемника составных сиг- 3р палов; на фиг. 2 — форма некоторых напряжений в схеме приемника.

В приемнике опознавание переданного сигнала осуществляется за к (к — число элементов составного сигнала) следующих непосредственно друг за другом шагов, в результате чего определяется к наибольших по абсолютному значению напряжений, поступающих с выходов согласованных фильтров н инверторов. Причем на каждом шаге определяется один наибольший элементарный сигнал, после чего напряжение опознанного сигнала отключается от входа решающего блока.

Предлагаемый приемник содержит согласованные фильтры 1, инверторы 2, решающий блок 8, преобразователь кодов 4 и хронизатор 5. Решающий блок имеет 2m входов и выходов (m — число используемых базистных функций). Выходы согласованных фильтров и инверторов подключены к 2m диодно-резисторным коммутирующим схемам, каждая из которых содержит резистор 6 и диод 7. Коммутирующая схема соединяет выход согласованного фильтра или инвертора с соответствующим входом решающего блока. Коммутирующая схема служит для отключения согласованных фильтров или инверторов от входа решающего блока и для запирания соответствующего канала решающего блока после опознания элемента посылки. Набор тригге311409

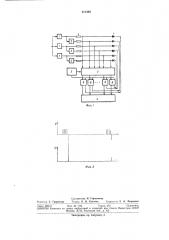

45 ров 8 служит для управления коммутирующими схемами. Все входы сброса триггеров объединены и подключены к хронизатору. Потенциальные выходы триггеров подключены к диодам коммутирующих схем. Импульсные выходы триггеров подключены к диодам коммутирующих схем. Импульсные выходы триггеров подключены ко входам преобразовагеля кодов. Хронизатор вырабатывает два импульсных сигнала (см. фиг. 2): пакеты импульсов 9, необходимые для проведения к шагов при опознании посылки, и импульсную последовательность 10 для сброса триггеров.

В момент, предшествующий опознанию очередной посылки, все триггеры находятся в начальном состоянии, при котором потенциалы на потенциальных выходах триггеров превосходят самое большое положительное напряжение, которое .может наблюдаться на выходах согласованных фильтров или инверторов.

Все диоды заперты, напряжения с выходов согласованных фильтров и инверторов через небольшие сопротивления резисторов поступают на выходы решающего блока.

В момент окончания сообщения на решающий блок от хронизатора поступает пакет импульсов из к коротких импульсов опроса.

Первый пришедший импульс вызывает срабатывание одного из каналов решающего блока и появление импульса на том его выходе, которому соответствует наибольший входной сигнал. При этом опрокидывается соответствующий триггер. Напряжение на его потенциальном выходе приобретает отрицательное значение, т. е. значение меньшее, чем самый низкий отрицательный потенциал, наблюдаемый на выходах согласованных фильтров. Отпирается соответствующий диод, и на вход сработавшего канала решающего блока, начиная с этого времени, действует постоянное отрицательное напряжение от потенциального выхода опрокинувшегося триггера. С приходом второго импульса опроса вновь происходит срабатывание решающего блока, при этом сравниваются 2т=1 входных сигналов и из них выбирается наибольший. Срабатывает соответствующий триггер, а с помощью коммутирующей схемы блокируется вход сработавшего канала решающего блока. После прихода к-го импульса оказывается опрокинутыми к триггеров 8, причем номера опрокинувшихся триггеров соответствуют номерам к наибольших по абсолютному значению элементов сообщения, которые и считаются опознанными. После прихода к-го импульса опроса в триггерах записывается номер опознанного сообщения в форме параллельного двоичного кода из 2т разрядов. Пришедшая из хронизатора импульсная последовательность для сброса триггеров сбрасывает все триггеры и переводит записанное в них число в преобразователь кодов.

Для описанного режима работы существенно, чтобы длительность импульсов опроса решающего блока и интервал между ними были достаточно малы, чтобы за время прохождения всего пакета из импульсов опроса напряжение на выходах согласованных фильтров не успевало существенно измениться. Если это требование не выполняется, то между выходами согласованных фильтров и входами инверторов необходимо включить специальные элементы промежуточного запоминания в виде накопительных емкостей и ключей сброса.

Предмет изобретения

Приемник составных сигналов, образуемых постоянным числом элементов, выбранных из биортогонального ансамбля, содержащий фильтр, согласованный с элементами составного сигнала, инверторы, решающий блок, преобразователь кодов и хронизатор, отличающийся тем, что, с целью увеличения возможности числа опознаваемых сигналов, повышения точности опознания и быстродействия системы передачи дискретных данных при одновременном упрощении схемного решения, между выходами согласованных фильтров и инверторов и входами указанного блока дополнительно включены диодно-резис горные коммутирующие схемы, а к выходам решающего блока подключен набор триггеров, причем потенциальный выход каждого триггера соединен с диодом коммутирующей схемы, а импульсный выход триггера соединен с преобразователем кодов.

Стиг. 1 сО

Составитель Н. Герасимова

Техрсд Л. В. Куклина Корректор Е. H. Миронова

Редактор T. Гаврикова

Типография, пр. Сапунова, 2

Заказ 2681/4 Изд. № 1125 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, )К-35, Раушская наб., д. 4/5