Устройство для преобразования десятичных чисел в двоичные и обратно

Иллюстрации

Показать всеРеферат

3II4

Со)оа Соеетскик

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К ПАТЕНТУ

Зависимый ат патента №вЂ”.Ч111х б 06т 5 02

Заявлена 18.11.1969 (№ 1315449 18-24)

11риар{{тет 06.V1.1968, ¹ ВП-12 132614, ГДР

Опубликовано 09.Vill.1971. Б{оллстен{ ¹ 24

Дата опубликования описания 20.XII.19 1

Комитет по делатл изобретений и откр)го{й при Совете Министров

СССР

У, 7, К 681.325.53(088.8) Авторы изобретения

Иностранцы

Инго Девальд, Герхард Христиаисмайер и Людвиг Бахмаин (Германская Демократическая Республика) Иностранная фирма

<ФЕБ Электронише Рехенмашинен» (Германская Демократическая Респуалика) Заявитель

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДЕСЯТИ IHblX ЧИСЕЛ

В ДВОИЧНЫЕ И ОБРАТНО

Изобретение относится к области автоматики {{ вычислптельнof{ техники и предназначено для преобразования целых и представляющих правильную дробь десятичных чисел в двоичные числа и обратно.

Известно устройство для преобразова{{{{я десятичных чисел как целых, так и представляющих правильную дробь в двоичные числа и обратно, содержащее сдвиговый регистр с кодопреобразователями; преобразование чисел в таком устройстве осуществляется за М тактов, если сдвиговый регистр содержит .)1 разрядов.

Для повышения быстродействия в предлагаемом устройстве выходы последних К разрядов сдвигового регистра соединены со входами обоих кодопреобразователей десятичного регистра первого разряда, выходы этих кодопреобразователей соединены со входами десятичного регистра того же разряда; К выходов кодопреобразователей десятичного регистра каждого предыдущего разряда соединены с

1(входами кодопреобразователей десятичного регистра последующего разряда; 1(выходов кодопреобразователей десятичного регистра последнего разряда соединены со входами первых К разрядов сдвигового регистра.

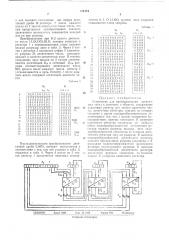

На чертеже изображена схема устройства.

Устройство содержит г11-разрядный сдвиговый регистр 1 для записи двоичных чисел, десятичные регистры 2 для записи 1-го, 2-го....

У-го разряда десятичных чисел, кодопреобразователн 3 и 4, К выходных цепей сдвиговага регистра 5, К выходных цснсй кодопреобразователей {), выходные цепи кодопреобразоватслсй 7, выходные цепи десятичных регистров 8.

Устройство работает следующим образом.

Содержимое сдвигового регистра 1 сдвигастся на К разрядов вправо. На колопреобра10 зователн 3 н 4 гиобого п-го разряда подается десятичное числа 7,, па цепям 8 н сигналы I,, ),, {,... l, ),t,. vo цепям {), соответству{о{ц{{е цифрам двончнога числа Е,{") илн Е,г) ). На кодопреооразователи 8 и 4 первого разряда пода{отся снгна.{ы lo„ lo. I „, по цепям г с послед{и{к разрядов сдвнгового рсгнстра 1. Сигналы l.ó), lë,..... l,ëл подаются с выходов кодопреобразователей 3 и 4 последнего Л)-га разряда по цепям 6 на входы первых К раз20 рядов сдвигающего регистра.

Двоичное число Е,, ) на выходах кодопреобразователя 8 и-го разряда соответствует выражению. е

Двоичное число Е)- > на выходах кодопреобразователя 4 и-ro разряда соответствует выраженшо:

Е„ г)=l) { 2л —, 1„г 2» — г — — l,.q 2ЗИ474

1 одопрсобразователь 8 любого и-го разряда выполняет операции, описываемые выражением (() Z„+ 10Еп

П . >

/ причем полученное десятичное число Z записывается по цепям 7 в соответствующий десятичн))й регистр 2. Цифры остатка от деления образуют двоичные единицы сигналов L„„

l„„ i „. Работа кодопреобразователя 4 любого и-го разряда описывается выражением (2) Е(2) Е (-,— 2 Z tt

Дробный остаток от деления образует десятичное число 2 и .

Для преобразования целого десятичного числа, цифры которого закодированы любым способом, в двоичное представление, число десятичных разрядов путем добавления дополнительных нулей преобразуют в число, кратное

V; при этом возникает i групп по N цифр в каждой. Эти группы, начиная со старших разрядов, вводят в десятичные регистры 2, причем веса внутри каждой группы равномерно убывают, начиная с 1-ro разряда устройства. Интервал между вводом предыдущей и последу И (ощей группы равен — тактам, причем в ка( ждом такте осуществляется одновременное преобразование в кодопреобразователях 8 всех разрядов, а также осуществляется сдвиг содержимого регистра 1 на К разрядов впраМ! во. Через тактов в регистре 1 оказываетl( ся ".àïèñàííûì двоичный эквивалент преобразуемого десятичного числа.

Для преобразования десятичного числа, представляющего правильную дробь, число разрядов после запятой путем добавления нулей приводится к целому числу, кратному N; при этом образуется t групп по Л(цифр в каждой. Эти группы, начиная с младшего разряда, вводят в десятичные регистры 2, причем веса внутри каждой группы равномерно возрастают в направлении от 1-го к последнему разряду устройства. Интервал между вводом (И предыдущей н последующей группы равен—

К тактам, причем В каждом такте осуществляется одновременное преобразование в кодопреобразователях 4 всех разрядов и сдвиг содержимого регистра 1 на К разрядов вправо.

Ч рез — тактов в регистре 1 оказывается записа)шым двоичный эквивалент десятичной дроби с точностью, зависящей от числа разрядов М в регистре 1, и с повышающимися в направлении сдвига весами двоичных разрядов.

Для преобразования целого двоичного чиT;(6:(((((а 1

2п0123456789

0 000

5555666677

00LLOOLL00,,:0

lÄ, =о /

),2 It

1 п2

l

l =-Е

„— (,2=0 Z „ (п--!,2=L Z „ п2

2233334444

7788889999

Х..С 0 OLL 0 OLL

1) 50

Результат работы при тех же условиях

0L OL OL PL 0 кодопреооразователей 4 приведен в табл. 2.

Таблица 2

Яп О 1 2 3 4 5 6 7 8 9

l.,, -0 „,,=о /,, е

Z„0482604826

Z1593715937

l2000LL000LL

12 —— 02 260482604Ь

О 0 LLL О 0 LLL

p p p p O LLLLL

П! сла в десятичное представление (c цифрами, закодированными любым способом), двоичное число вводится в регистр 1 так, что веса двоичных разрядов повышаются в направлении

Л! сдвига. В течение — тактов проводится одК новременное преобразование в кодопреобразователях 4 всех разрядов, после чего осуществляется сдвиг содержимого регистра 1 на К разрядов. Десятичное число, состоящее из Ж десятичных цифр, сосчитывается группами с

1(одо преобразователей 4 (по цепям 7, причем веса десятичных разрядов повышаются, начиная с 1-ro разряда устройства. Регистры 2 ycA1 i танавливаются снова в нуль, Через —,— тактов

К преобразование окончено.

Для преобразования правилыюго дробного двоичного числа в десятичное, двоичная дробь

Л1

20 вводится в регистр 1. Через тактов, в теК чение которых осуществляется одновременное преобразование в кодопреобразователях 8 всех разрядов и сдвиг содержимого регистра на К разрядов, по цепям 7 сосчитывается десятичное число, начиная с группы наибольше1-о веса, причем веса десятичных разрядов уменьшаются, начиная с 1-го разряда устройства. Регистры 2 снова устанавливаются в

;И 1 нуль. Через — — тактов получаем десятичный

К эквивалент двоичной дроби с точностью, зависящей от i.

При К=2 результат работы кодопреобразователя 8 любого и-го разряда, т. е . 1-го и

2-го в зависимости от входных сип(алов! „ и l„.(, приведен в табл. 1 (обозначение L соответствует двоичной единице) 311474

При кодировании десятичного числа двоич11о-десятичным кодом 8 — 4 — 2 — 1, цепи 8 имеют четыре шины а, b, с, d, а цепи 7 — четыре шины а, b, с, d . В этом случае работа кодопреобразователей 8 описывается следующими уравнениями: и =-.ln 1.1 I„ 1,2 (а,, В :, C)

b =-1„1,! ln !., ln. 11 1„.1,- (а/ в с)1/1„1,2 (а Ьс) с =ln 1 а, ln 11 а b с,/1„1,! 1„1, bQ

, 1„1, 1„1,2 (Ь r Q/а с)

: — lл — 1, 1 ln — 1,2 b V ln 1, 1 lа . 1,2 Ь, lа 2 Ь С \/ ч 1л — 1,1 ln. 1,2 Ь C ln .! b Ñ L, lп — 1 1 ln — 1 2 b С

1„1-- d

ln2 — I((- 1 С i 1»- 1,! c

Работа кодопреобразователей 4 описывается следующими уравнениями: а —.ln f,! (b.ñ й, Ьсй),/1„.. f,! (Ьсй, ай) Ь . -ln 1,1.(Ь с йл1bd)gin f,f(abd /ïdßbcd с ==ln 1,1(а (Ьсй, bcd), 1„1,!(аЬс 7bcd,. bcd) и — ln — 1,2

Ри Таблица 3 аюю !ю!

abed

Dfoo: IООL

П!00

ООLO

01 ОL

0001

ОООО

ООLL

Dfo |!! и, L0 O O

0 LI L

100 L

0 Loo

L000

00 1.0

0000

abed

Rf а ь с с!

Таблица 4

Ro!

02 !О!

0000

0000

i. OLOL

00L0

1.00 О

ООLO

OL0L

О LLO

000 L

O LO L

ООLL

0000 по

01.00

Dfo

0000

0000

00L0

00 LL

0 LLL

0000, 0 О О О, 0101

0001

0 1.11

O LL0 оооо, Dfo

1 ÎOL и„-!

OL00

0 0 L0

L0 0 0

L00 L

О О О О)

О I.Î 1.f

O00L

O IO1 оо oof

D(o

001.0

П(ю-"

001 1.

0000

О !

3

5

7

9 !

О !

1 !

2 !

3 !

4 !

5 !

6 !

7 !

19

0 00000000000000

OLOOOOOOOOOOOO

2 !! LООL0000000000

3 I 0LL00LОООООООО

4 OLOLLOOL000000

5 OOOLOLLOOLOOOO

6 ОООООLОLLООLОО

7 ОООООООLОLI 001.

8 ÎL0000000LOLLO

9 f 000L0000000LOL

10 O LOO0 L0000000L !! (1LОIОООLОООООО

12 1ОLIОIОООLОООО !

3 О О LО LLО LО О О LО О

14 LOОOI. О I.LOLOО О L

О LLOLOOOLLOLOO !

О О О L L О 1 О О О 1. 1 О L

О О О О О LI.О LО О О LL

О 1 О О О О О L L О L О О О

О 1.0 LО О О 0 О LLО LО

000 LO L00000 LL0

LL000L0L00000 L

LLLL0OOLOL0000

О О L 1. L 1. О О О L О I. О О

О О О О LLLLО О О 1 О L

О О О О О О LLLLО О О L

О LО О О О О О LLLLО О

1 1. О L О О О О О О L 1. L I

1. LLLO Lo О О О О О LL

О О 1. L L L О LО О О О О О

0000LLLLO L0000

000000LLLLO L00

0 0 0 0 0 0 0 0 L L L LO L

0000000000LL1.L

0 L0000000000 L1.

О L 0 L O О О О О О О О О О

I LОLО LОООООООО

10 !

1,1 — а /bc . Ьй

ln2=n :/1n. 1,! (Ьс, rd)g/bcdQbrd

Преобразование заданного целого десятичного числа 8913 в двоичное число в последовательно-параллельном режиме работы устройства отражено в табл. 3;

В регистры 2 1-го и 2-го разряда (I(=2) записывают сначала тысячный и сотенный разряды (D 1000, D100) заданного числа, закодированные В,двоичном виде. 3а семь такА1 тов () образуется двоичный эквивалент этого числа. Затем в регистры 2 вносятся десятичный и единичный разряды, и еще через 7 тактов в регистре 1 оказывается записанным двоичный эквивалент числа 8913 с понижа1ощнмпся слева направо весами разрядов.

Отдельные шаги процесса преобразования двоичной дроби О, 011 01 00011 О1 00 в соответству1ощую десятичную дробь 0,409423... отражены на табл. 4.

В регистре 1 записана двоичная дробь; веса разрядов поги1жаются слева направо. Регистры 2 установлены в нуль. Через 7 тактов с регистров 2 снимаются оба высших разряда десятичной дроби (в двоичной форме). После установки регистров 2 в нуль, через 7 тактов

abed

00LO

000L

0 0 L0

О 1.О 1.

ООLL.

00 LLI

0000! 5114 4 с нпх снимают следующие две цифры десяти шой дроби. В регистре 1 после каждого цикла из 7 тактов ооразустся такое число, что при продолжении преобразования точность десяти (ного эквпв(1лснта повышается кaæäû(( раз на два разряда.

Преобразование при К-2 целого двоичного числа 1.LOLOOLOLO, которое записано в регистре 1 с повышающимися слева направо весами разрядов дано в табл. 5. Через " тактов с регистра 2 снимается цифра 2 ед>иничпого разряда D, десятичного числа, закодированного в двоичпо-десятичном коде. В течение следующих двух циклов по 5 тактов сосчитываютсЯ десЯтичный D(p и сотенный D!pp Разряды соответствующего десятичного числа

842, причем после каждого цикла регистр 2 устанавливается в нуль. Регистр 1 после каждого цикла содержит остаточное двоичное число. веса разрядов

Таблица

1> аЬс(!! (>

J02 01 (оооооооооо

D,„

0 L00000000

0 0 0 L0 0 O 0 0 0

J 00000 L000 0

0000000 L00

ILLoooooono

100LLОООООО

О О О 0 LLО О О О

0 00000 LL00

00000000 LL

D — а и>

LL00ООООО0

011.LОООООО

00 0 1 LLOOOO

000001LIOO

О О О О О О О I. 1.1

О LО О О О О 0 О L

I.LO Lo 0 0 0 0 0

ООI.L010000

О О О О 1. 1. 0 I. 0 О таб 1ица б> а b с 1!

0000

102 101

ООООООLLOI

О Lo Lo О Lo LL

0 0 0 LO LO 0 LO

LООООLОLО0

LОLООООLОL

LО LО 1.0 О О О 1

Предмет изобретения

Устройство для г(ppoop33o(:3((((51 дссятич»((п)сел в двоичные и обрат((о, содержащее

30 сдвнговый регистр для за(ион двоичного числа, десятичные регистры, каждый из которы.: соединен с двумя кодопреобразователями, от(((>(aiouIeecv тем, что, с целью повышения ub(стродействия, выходы последних К разрядов

38 сдвпгового регистра соединены со входQ. >(((Ооопх кодопрсобразоватслсй десяти (ного р гпстра первого разряда, выходы этих кодопрсобразователей cocz((((e((((со входами десяти!ного регистра того жс разряда; К выходов .!0 кодопреобразователей дссятпч(юго регистра каждого предыдущего разряда соединены с К выходамп кодопреобразователсй десятичного регистра последующего разряда; К выходов кодопрсобразоватслей десятичного регистра

48> после щего разряда соединены со входами первых К p;(3ps(дои сдвигового регистра.

О О Lo Lo Lo 0 0

001.0

ООООLОLОLО

000000LOL0

00000000L0

O L0 0 0 0 0 0 0 0

OI.ОО

D„, 0 00 L00000 0

0 0000 Looon

0 0 0 0 0 0 0 L0 0

000000000L

0000000000

I,O0O

D>nn

Последовательность преобразования десятичной дроби 0,6875, которая выполняется в соответствии с тем, как это указано в табл. 3, отражена в табл, 6. Через 4 цикла по 5 тактов регистр 1 заполняется двоичным эквиваRo

Подппснос

1 (зд .Хо. !102

Т((ра)к 473

ЦНИИПИ Заказ 4382

Загорская типографи>1

О

2

4 ь

8

9 !

О

J! !

13 !

J8

00 LI.

00I L

ООLO

0 О О 1.

OIOI

000 L

ОООО

00LO

0000 лентом Г), 1 0 1 1.00, причем повышаются слева направо. о

9, 1

1О

Э

I>

8

1б !

О

11

J > ! >

14 го !б

16

17 !

19

OLOL оооо оооо оооо, о о оо

01 Е1 оооо оооо оооо оо о о, Loon

I 0LOL оооо оооо оооо

О 1Л.О

O LLL оооо оооо оооо оооо