Устройство синхронизации

Иллюстрации

Показать всеРеферат

СПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

320942

Сова Советоких

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 04.Ч.1970 (№ 1438413/26-9) с присоединением заявки №

Приоритет

Опубликовано 04,XI.1971. Бюллетень № 34

Дата опубликования описания 25.1.1972

МПК Н 041 7/02

Комитет ло делам изобретений и открытий лри Совете Гнннотpов

СССР

УДК 621 394 662 2(088 8) Авторы изобретения

А. A. Килна и Б.-Ю. Б. Бинкаускас

Институт физики и математики АН Литовской ССР

Заявитель

УСТРОЙСТВО СИНХРОНИЗАЦИИ

Изобретение относится к технике передачи данных и может быть использовано в системах связи в качестве устройства формирования тактовых сигналов.

Известны устройства синхронизации, содержащие фазовый дискриминатор, интегратор. фильтр нижних частот, регулируемую линию задержки, блок совпадения, блок формирования импульсов и триггер запуска. Однако эти устройства имеют недостаточную точность фазирования выходного сигнала относительно входного, так как период выходного сигнала определяется как сумма номинального значения периода и временного рассогласования между входными и выходными импульсами в предыдущем периоде.

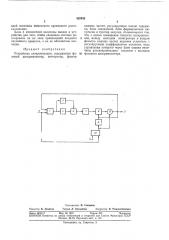

Целью изобретения является повышение очности синхронизации. Для достижения этой цели между выходом интегратора и входом фильтра нижних частот включен усилитель с регулируемым коэффициентом усиления, вход управления которого через блок оценки величины рассинхронизации соединен с выходом фазового дискриминатора.

На чертеже приведена блок-схема предложенного устройства.

В устройстве синхронизации дискриминатор

1 входами подключен к шине 2 входных сигналов и выходу 8 устройства. Выход дискриминатора 1 соединен с входами блока 4 абсолютной величины и интегратора 5, выходы которых соединены с входами усилителя б с управляемым коэффициентом усиления. Выход усилителя б через фильтр 7 нижних частот подключен к управляющему входу регулируемой линии 8 задержки, импульсный вход которой через формирователь 9 импульсов соединен с единичным выходом триггера 10.

Единичный вход триггера 10 подключе т к тпипе 2 входных сигналов, а нулевой вход—

10 к шине 11 стоп-импульса. Вентиль 12 импульсным входом соединен с выходом линии 8 задержки, а потенциальным — с единичным выходом триггера 10.

Устройство работает следующим образом.

Первый входнон импульс ставит триггер 10 в единичное состояние. Импульс, сформнрованпьш формирователем 9, поступает на вход регулируемой линии 8 задержки, выход 8 и на вход фазового дискриминатора 1, Управляю20 щее напряжение линии 8 задержки при этом равно нулю, поэтому второй выходной импульс устройства появляется через номинальное значение периода повторения.

Фазовый дискриминатор 1 вырабатывает

25 напряжение, пропорциональное разности интервала времени входного и выходного импульсов, поэтому длительность второго выходного периода равна сумме номинального значения периода и интервала времени, пропор30 ционального указанной разности, а коэффициент пропорциональности является функ320942

Составитель Н. Степанов

Техред Л. Богданова Корректор Н. Рождественская

Редактор В. Левятов

Заказ 3932717 Изд. № 1579 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 цией величины моментного временного рассогласования.

Блок 4 абсолютной величины введен в устройство для того, чтобы следящая система реагировала не на знак производной входного случайного процесса, а на ее абсолютное значение.

Предмет изобретения

Устройство синхронизации, содержащее фазовый дискриминатор, интегратор, фильтр нижних частот, регулируемую линию задерж. ки, блок совпадения, блок формирования импульсов и триггер запуска, отличаюи ееся тем, что, с целью повышения точности синхрониза5 ции, между выходом интегратора и входом фильтра нижних частот включен усилитель с регулируемым коэффициентом усиления, вход управления которого через блок оценки величины рассинхронизации соединен с выходом

10 фазового дискриминатора.