Устройство для умножения частоты следованияимпульсов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 32!8!9, ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союа Советских

Социалистических

Республик

Зависимое от авт, свидетельства №

Заявлено 03.111.1969 (№ 1308242/18-10) с присоединением заявки №

Приоритет

Опубликовано 19.XI.1971. Бюллетень № 35

Дата опубликования описания 31.1.1972

МПК G 061 23/10

IC0MHT8I А0 делам изобретений и открытий ори Совете Министров

СССР

УДК 621.317.761 (088.8) Авторы изобретения

И. В. Кузьмин, В. Т. Рябуха и В. Н. Чинков

Заявитель

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ

Изобретение относится к области электроизмерительной техники.

Известное устройство для умножения частоты следования импульсов, содержащее блок выделения периода входной частоты и управления, запоминающий регистр, сумматор, вентили, схему «ИЛИ» и генератор образцовой частоты, характеризуется суженным диапазоном умножаемых частот и усложненной схемой.

Предлагаемое устройство отличается от известных тем, что в нем между запоминающим регистром и сумматором включены вентили переноса, импульсные входы которых связаны через схему «ИЛИ» с выходами блока управления и сумматора, счетные входы триггеров которого соединены через вентиль с выходом генератора образцовой частоты.

Такое выполнение устройства позволяет расширить диапазон умножаемых им частот и упростить его схемную реализацию.

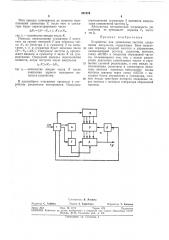

На чертеже показана блок-схема описываемого устройства, состоящего из блока 1 выделения периода и управления, запоминающего регистра 2, сумматора 8, генератора 4 образцовой частоты, вентилей 5 переноса, схемы «ИЛИ» б и вентиля 7.

Выход вентиля 7 подключен к установочным входам разрядов сумматора 8, соответ2 ствующих вводу коэффициента умножения К в требуемом коде в сумматор 3 на суммирование.

Регистр и сумматор соединены поразрядно вентилями 5 переноса так, что число из регистра 2 в сумматор 3 переносится на вычитание.

В исходном состоянии регистр 2 и сумматор 3 находятся в «нулевых состояниях», вен10 тиль 7 закрыт.

Работа устройства начинается с момента поступления на вход блока 1 первого импульса, соответствующего началу периода Т входного сигнала (,. С этого времени импульсы частоты fo поступают на входы регистра 2 на суммирование и сумматора 8 — на вычитание. После поступления второго импульса частоты f.„óñòðîéñòâî не реагирует на импульсы входной частоты f .

В результате в регистре 2 будет записано число N„„=Т„ fo, а в сумматоре 3 — число (2" — N„), здесь и — количество разрядов регистра и сумматора. С этого времени им2S пульсы частоты fo через открытый вентиль 7 непрерывно поступают на установочные входы сумматора 8. После прихода каждого импульса частоты fo к показаниям сумматора добавляется число К в двоичном коде, 321819

Предмет изобретения

Составитель В. Лившиц

Текред 3. Тараненко

Редактор С. Хейфиц

Короектор Т. Китаева

Заказ 36/3 Изд. М 1712 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Этот процесс повторяется до момента переполнения сумматора 8, после чего в сумматоре будет зарегистрировано число

gN — (Яп — N + j< . К) (N где i — количество вводов числа К.

Импульс переполнения сумматора 2 поступает на группу вентилей 5 для переноса числа N из регистра 2 в сумматор 3 на вычитание, т. е. в сумматоре будет записано число (2" — N„yhN ). Импульсы частоты fp продолжают вводить в сумматор 3 число К на суммирование. Очередной импульс переполнения появится, когда поступит число импульсов

12 К) Nx « А/1» где i2 — количество вводов числа К после появления первого выходного импульса устройства.

В дальнейшем описанные процессы в устройстве циклически повторяются. Импульсы с переполнения сумматора 3 являются импульсами умноженной частоты f„.

Абсолютная методическая погрешность умножения не превышает периода То частоты fp.

Устройство для умножения частоты следования импульсов, содержащее блок выделеl0 ния периода входной частоты и управления, запоминающий регистр, сумматор, вентили, схему «ИЛИ» и генератор образцовой частоты, отличающееся тем, что, с целью расширения диапазона умножаемых частот и упро15 щения схемной реализации, в нем между запоминающим регистром и сумматором включены вентили переноса, импульсные входы которых связаны через схему «ИЛИ» с выходами блока управления и сумматора, счет20 ные входы триггеров которого соединены через вентиль с выходом генератора образцовой частоты,