Патент ссср 321897

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

k АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Саветоких

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 04.1.1970 (№ 1391717/26-9) с присоединением заявки № 1397343 26-9

Приоритет

Опубликовано 19.XI.1971. Бюллетень ¹ 35

Дата опубликования описания 31.1.1972

МПК H 021т 7/14

Комитет по делам изобретений и открытий ори Совете Министров

СССР

УДК 621.396.669 (088.8) Авторы изобретения О. Л. Венедиктов, В, В, Донцов, Э. В. Лысенко и А. И. Чупринов

Заявитель

УСТРОЙСТВО ДЛЯ ПОВЫШЕНИЯ ПОМЕХОЗАЩИЩЕННОСТИ

Известны устройства для повышения помехозащищенности сигнальных цепей импульсных и потенциальных схем, работающие по принципу ограничения сигнала.

В таких устройствах повышение помехозащищенности путем увеличения порога срабатывания при подаче на их входы сигнала логического «О» и помехи, увеличивающей этот сигнал, ведет к снижению помехозащищенности устройств при подаче на их входы полезного сигнала логической «1».

Целью изобретения является повышение помехозащищенности без увеличения мощности входного сигнала. Это достигается тем, что база одного из ключевых транзисторов подсоединена ко входу устройства через инвертирующий транзисторный каскад, а база другого— через полупроводниковый диод.

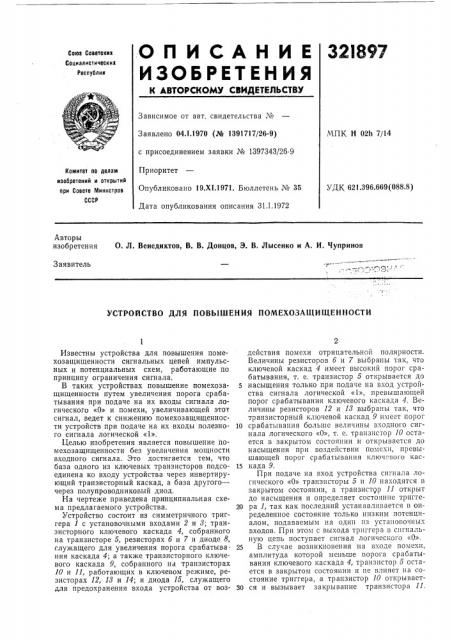

На чертеже приведена принципиальная схема предлагаемого устройства.

Устройство состоит из симметричного триггера 1 с установочными входами 2 и 8; транзисторного ключевого каскада 4, собранного на транзисторе 5, резисторах б и 7 и диоде 8, служащего для увеличения порога срабатывания каскада 4; а также транзисторного ключевого каскада 9, собранного на транзисторах

l0 и 11, работающих в ключевом режиме, резисторах 12, И и 14; и диода 15, служащего для предохранения входа устройства от воздействия помехи отрицательной полярности.

Величины резисторов б и 7 выбраны так, что ключевой каскад 4 имеет высокий порог срабатывания, т. е. транзистор 5 открывается до

5 насыщения только при подаче на вход устройства сигнала логической «1», превышающей порог срабатывания ключевого каскада 4. Величины резисторов 12 и 18 выбраны так, что транзисторный ключевой каскад 9 имеет порог

10 срабатывания больше величины входного сигнала логического «О», т. е. транзистор 10 остается в закрытом состоянии и открывается до насыщения при воздействии помехи, превышающей порог срабатывания ключ:.восо кас15 када 9.

При подаче на вход устройства сигнала логического «О» транзисторы 5 и 10 находятся в закрытом состоянии, а транзистор 11 открыт до насыщения и определяет состояние тригге20 ра 1, так как последний устанавливается в определенное состояние только низким потенциалом, подаваемым на один пз устапогочных входов. При этом с выхода триггера в сигнальную цепь поступает сигнал логического «О».

25 В случае возникновения на входе помехи, амплитуда которой меньше порога срабатывания ключевого каскада 4, транзистор 5 остается в закрытом состоянии и не влияет на состояние триггера, а транзистор 10 открываетЗО ся и вызывает закрывание транзистора П.

32I897

Составитель А. Мерман

Техред 3. Тараиеико

Корректор О. Волкова

Редактор Т. Юрчикова

Заказ 26/16 Изд. № 1723 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

При этом состояние триггера не изменяется, т. е. помеха на выход устройства не проходит.

Этим достигается высокая помехозащищенность при наличии на входе устройства сигнала логического «0».

При подаче на вход устройства сигнала логической «1» транзистор 5 открывается и вызывает изменение состояния триггера 1. При этом с выхода триггера в сигнальную цепь поступает сигнал логической «1». Транзистор 10 открывается, а транзистор 11 закрывается и не влияет на состояние триггера, В этом случае при возникновении на входе устройства помехи, понижающей амплитуду входного сигнала, транзистор 5 закрывается и не влияет на состояние триггера, состояние транзисторов 10 и 11 не изменяется, поэтому помеха на выход устройства не проходит.

Этим достигается высокая помехозащищенность при наличии на входе устройства сигнала логической «1».

5 Предмет изобретения

Устройство для повышения помехозащищенности сигнальных цепей импульсных и потенциальных схем, содержащее управляемый

10 симметричный триггер с ключевыми транзисторами, шунтирующими соответствующие активные элементы триггера, отличающееся тем, что, с целью повышения помехозащищенности без увеличения мощности входного сигнала, 15 база одного из ключевых транзисторов подсоединена ко входу устройства через инвертирующий транзисторный каскад, а база другого— через полупроводниковый диод.