Устройство формирования синхронизирующих последовательностей

Иллюстрации

Показать всеРеферат

О П И СА Н И Е

ИЗОБРЕТЕНИЯ

Союз Ссеетск1к

Сонкалкстккескни

Республик

Зависимое от авт. свидетельства ¹

Заявлено 20. 1/111.1969 (№ 1358370/26-9) с присоединением заявки ¹

Приоритет

Опубликовано 19.Х1.1971. Бюллетень № 35

Дата опубликования описания 26.1.1972

МПК Н 0417/01

Комитет по делам изобретений и открытий при Совете Министров

CCGP

УДК 621.394.662.2 (088.8) Авторы изобретения

А. С. Альтман и О. И. Маркин

Заявитель

УСТРОЙСТВО ФОРМИРОВАНИЯ СИНХРОНИЗИРУЮЩИХ

ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Предлагаемое устройство относится к системам синхронизации и предназначено для формирования импульсных последовательностей, синхронных с внешним сигналом и сохраняющих синхронность с сигHBJIoivf при кратковременных его пропаданиях.

Известны устройства формирования синхронизирующих последовательностей, содержащие блок фазовой автоподстройки частоты (ФАПЧ), блок стартстопной синхронизации, состоящий из дешифратора с и формирователями служебных импульсов, делителя частоты, выполненного на триггерах, и блока переключений.

Известные устройства обладают тем недостатком, что при первоначальном вхождении в связь или после длительного нарушения связи в силу своей инерционности требуют определенного времени вхождения в синхро. низм.

С целью уменьшения времени вхождения в синхронизм в предлагаемом устройстве один из входов блока переключений через блок фазовой автоподстройки частоты подключен ко входу устройства, а другой вход блока переключений подключен ко входу устройства непосредственно, при этом один из выходов блока фазовой автоподстройки частоты подключен через блок переключений к делителю частоты блока стартстопной синхронизации, а другой выход блока фазовой автоподстройки частоты — непосредственно к делителю частоты блока стартстопной синхронизации, выходы которого своими и формирователями служеб5 пых импульсов подключены ко входу устройства обработки информации.

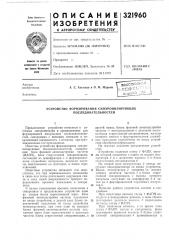

На чертеже показано предлагаемое устройство.

Устройство содержит схему 1 ФАПУ, выхо10 ды которой соединены с одним из входов коммутатора 2 и с делителем частоты 8 в блоке стартстопной синхронизации 4.

На второй вход коммутатора 2 сигнал поступает непосредственно со входа устройства.

15 Выход коммутатора 2 соединен со входом

«сброс» делителя частоты 8 в блоке стартстопной синхронизации, с выхода которого импульсы поступают на дешифратор б и затем íà и формирователей служебных пмпуль20 сов 6.

Принцип работы устройства состоит в следующем.

При отсутствии сигнала схема 1 ФАПЧ находится в асинхронном режиме, а цепь сброса

25 трнггерного делителя частоты 8 подключена ко входу схемы i ФАПЧ.

При появлении сигна" ÿ.,,в то время пока схема 1 ФАПЧ входит в спнхронизм, фаза триггерного делителя частоты 8 блока старт30 стопной синхронизации 4 привязывается к

321960

Составитель Е. Чуркин

Техред Е. Борисова

Корректор Н. Шевченко

Редактор Т. Морозова

Заказ 3947/10 Изд. № 1766 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типографии, пр. Сапунова, 2 первому же маркеру с точностью до периода

-частоты опорного генератора (Uor) Одновременно происходит привязка к маркерному сигналу и последовательности служебных импульсов, так как их фаза однозначно определяется фазой делителя частоты 3.

После того, как схема ФАПЧ вошла в синхронизм (частоты опорных генераторов на приемной и передающих сторонах равны, а фазы маркерного сигнала «М», приходящего на вход ФАПЧ и сигнала «М», формируемого схемой ФАПЧ, совпадают), коммутатор 2 переключает цепь сброса делителя частоты 3 со входа ФАПЧ (сигнал U,„) на ее выход (сигнал U„,,).

Последовательность служебных импульсов

U — с/„сохраняет синхронность с сигналом с/м,ь поступающим по цепи сброса. В этом режиме устройство синхронизации реализует фильтрующие и астатические свойства ФАПЧ, В случае длительных пропаданий сигнала коммутатор 2 производит подключение цепи сброса делителя частоты 8 с выхода на вход

ФАПЧ (обратное переключение).

Время, прошедшее с момента пропадания сигнала до момента обратного переключения, может быть выбрано с помощью времязадак>щей схемы, входящей в состав.коммутатора 2.

Предмет изобретения

5 Устройство формирования синхронизирующих последовательностей, содержащее блок фазовой автоподстройки частоты, блок стартстопной синхронизации, состоящий из дешифратора с и формирователями служебных им10 пульсов, делителя частоты, выполненного на триггерах, и блока переключений, отличаюи4ееся тем, что, с целью уменьшения времени вхождения в синхронизм, один из входов блока переключений через блок фазовой авто1S подстройки частоты подключен ко входу устройства, а другой вход блока переключений подключен ко входу устройства непосредственно, при этом один из выходов блока фазовой автоподстройки частоты подключен через

20 блок переключений к делителю частоты блока стартстопной синхронизации, а другой выход блока фазовой автоподстройки частоты— непосредственно к делителю частоты блока стартстопной синхронизации, выходы которо25 го своими и формирователями служебных импульсов подключены ко входу устройства обработки информации.