Устройство фазирования и регенерации для трансформатора скорости дискретных сигналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

321962

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 24.VI.1970 (Ме 1451986/26-9) с присоединением заявки №

Приоритет

Опубликовано 19.Х1.1971. Бюллетень № 35

Дата опубликования описания 26.1.1972

МПК Н 04t 7/02

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 621.394.42(088.8) Автор изобретения

Г. А. Полиевский

3 аявитель

УСТРОЙСТВО ФАЗИРОВАНИЯ И РЕГЕНЕРАЦИИ

ДЛЯ ТРАНСФОРМАТОРА СКОРОСТИ ДИСКРЕТНЫХ СИГНАЛОВ

Изобретение относится к области электросвязи.

Известны устройства фазирования и регенерации для трансформаторов скорости дискретных сигналов, в которых для выделения синхросипнала используются зна коперемены ото всех информационных подканалов.

Недостатками известных устройств является низкая помехоустойчивость.

С целью повышения помехоустойчивости в 10 предлагаемом устройстве входы управления фазовых дискриминаторов подключены к коммутатору, между коммутатором и управляемым делителем включен формирователь сетки фаз опорных импульсов, а входы «опереже- 15 ние» и «отставание» управляемого делителя подключены ко входам сброса обоих счетчиков, причем потенциальные выходы счетчиков соединены со входом запрета обоих одноименных схем «НЕТ». 20

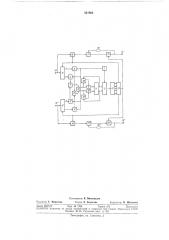

На чертеже приведена блок-схема предлагаемого устройства.

Задающий генератор 1 соединен со входом управляемого делителя 2 и входами схем «И» 25

8, 4 и 8, 4 и так далее всех подканалов, вторые входы схем «И» 8, 4 каждого подканала подключены к выходам «+» и « — » фазовых дискриминаторов 5, 5 соответствующего подКанала. 30

Выходы всех схем «И» 8, 8 и т. д. подсоединены к схеме «ИЛИ» б, выходы всех схем

«И» 4, 4 и т. д. подсоединены к схеме «ИЛИ»

7. Выходы схем «ИЛИ» б и 7 подключены ко входам схемы «ИСКЛЮЧИТЕЛЬНΠ— ИЛИ»

8. Выходы «+» и « — » схемы 8 соединены со входом схемы «НЕТ» 9 и входом счетчика 10.

Потенциальные выходы счетчиков 10 и 10 подключены ко входам запрета схем «НЕТ»

9 и 9, выходы которых включены на входы

«+» и « — » реверсивного счетчика 11. Выходы

«+» и « — » реверсивного счетчика 11 соединены с одноименными входами управляемого делителя 2, а его выход подключен к формирователю сетки фаз опорных импульсов 12, выходы формирователя 12 соединены с коммутатором фаз 18. Выходы коммутатора фаз

18 подключены ко входам управления фазовых дискриминаторов 5, 5 всех подканалов, общий выход коммутатора 18 соединен со входом управления вентилей 14, 14 и т. д. всех подканалов. Выходы вентилей 14, 14 ,и т. д. подключены к выходным клеммам устройства 15, 15 и через линию задержки 1б, lб соединены со входом сброса триггеров 17, 17 . Выходы триггеров 17, 17 подсоединень ко входам вентилей 14, 14, входы триггеров

17, 17 подключены к выходу узлов стробирования 18, 18, входы управления узлов 18, 18 соединены с выходами коммутатора 18, входы

321962 узлов 18 и 18 подсоединены ко входным клеммам устройства 19, 19 и входам соответствующих фазовых дискриминаторов 5, 5 .

Устройство работает следующим образом.

Постоянные фазовые сдвиги между подканалами устраняются выбором оптимальной фазы для каждого подканала посредством коммутатора 18. Так как кроме постоянных фазовых сдвигов существуют и переменные сдвиги, вызванные шумами и эффектом многолучевости, то с выхода, например, «+» или

« — » дискриминатора 5 поступают на входы схем «И» 8 и 4 импульсы различной длительности, которая пропорциональна фазовому сдвигу входного сигнала относительно фазы опорного напряжения с коммутатора 18.

На выходах схем 8 и 4 получаются «пачки» импульсов частоты задающего генератора, соответствующие квантованному значению фазовых сдвигов. Указанные «пачки» импульсов с выходов схем 8, 8 и 4, 4 суммируются по времени в схемах б и 7 только в том случае, если имеется временной сдвиг между этими

«пачками» импульсов, реализующими эффект, пропорциональной переменной коррекции фазы.

Если же «пачки» импульсов от различных подканалов приходят одновременно, то на выходе схем «ИЛИ» б, 7 действуют «пачка» из наибольшего числа импульсов. С выходов схем б и 7 «пачки» импульсов, соответствующие одноименному суммарному фазовому сдвигу сигналов с постоянным запаздыванием поступают на схему «ИСКЛЮЧИТЕЛЬНО—

ИЛИ», которая вычисляет разность между суммарным значением фазовых сдвигов в сторону «опережения» и «отставания».

С выхода схемы 8 импульсы «опережения» или «отставания» поступают на счетчик 10 или 10 и через схему «НЕТ» 9 или 9 на входы реверсивного счетчика 11. Схемы «НЕТ»

9 и 9 пропускают импульсы только в том случае, когда счетчики 10 и 10 полностью заполняются, так что выходной потенциал с последнего триггера счетчиков 10 и 10 открывает схему «НЕТ» 9 или 9 . Каждым импульсом с выхода реверсивного счетчика 11 производится сброс счетчиков 10, 10, что позволяет при качании фазы одного из подканалов вследствие многолучевости ввести дополнительную инерционность для предотвращения ложной подстройки фазы.

Такое выполнение устройства позволяет

5 демпфировать действия быстрых фазовых сдвигов на управляемый делитель, а также получить характеристику с экспоненциально взвешенным усреднением, тогда как интегрирование посредством реверсивного счетчика

10 приводит к пропорциональному усреднению.

Первая регенерация сигнала в каждом подканале производится на узлах стробирования

18, 18, отрегенерированный импульс с выхода

18, 18 запоминается на триггерах 17, 17, уп15 равляющих вентилями 14, 14 . При наличии сигнала на триггерах 17, 17 импульс с общего выхода коммутатора 18 выделяется на выходе вентилей 14, 14 и через линию задержки lб, lб установит триггеры 17, 17 в нуле20 вое положение. При поступлении отрегенерированного импульса с узлов 18, 18 триггеры

17, 17 установятся опять в единичное положение.

П р ед м ет изобретения

Устройство фазирования и регенерации для трансформаторов скорости дискретных сигна30 лов, содержащее в каждом подканале фазовый дискриминатор, две схемы «ИЛИ», узел стробирования, триггер, вентиль с линией задержки, а в групповой части — задающий генератор, коммутатор, управляемый делитель

35 с двумя входами на «опережение» и «отставание», реверсивный счетчик, логические схемы «ИЛИ», «НЕТ» «ИСКЛЮЧИТЕЛЬНОИЛИ» и два счетчика со сбросом, отличающееся тем, что, с целью повышения помехоустой40 чивости, входы управления фазовых дискриминаторов подключены к коммутатору, между коммутатором и управляемым делителем включен формирователь сетки фаз опорных импульсов, а входы «опережение» и «отстава45 ние» управляемого делителя подключены ко ,входам сброса обоих счетчиков, причем потенциальные выходы счетчиков соединены со входом запрета обоих одноименных схем

«НЕТ».

Составитель К. Виноградов

Редактор T. Морозова Тсхред Е. Борисова Корректор H. Шевченко

Заказ 3947/12 Изд. № 1766 Тираж 473 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий прн Совете Минисгроз СССР

Москва, 5К-35, Раушская наб., д. 4 5

Типография, пр. Сапунова, 2