Разряд динамического регистра сдвига

Иллюстрации

Показать всеРеферат

3247II

ОП И САН И6

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Рес|тублин

Зависимое от авт. свидетельства №

М. Кл. Н 03k 19/08

Заявлено 26.1 I.1969 (№ 1321058!18-24) с присоединением заявки М

Приоритет

Комитет по делам изобретений и открытий

УДК 681.326.33 (088.8) Опубликовано 23.XII.1971. Бюллетень № 2 за 1972

Дата опубликования описания 25.11.1972 при Совете Министров

СССР 1 «вЂ” ..2к

Б. В. Кузнецов, Г. С. Галахтин и Ю. А. Уральский --1-..:;. „ -,,-, 1:-..

Авторы изобретения

Заявитель

РАЗРЯД ДИНАМИЧЕСКОГО РЕГИСТРА СДВИГА

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в цифровых вычислительных машинах и различных логических устройствах.

Известные динамические регистры сдвига содержат источники питания постоянного тока, тактовые источники питания и диодно-резисторные логические схемы с запоминающими конденсаторами.

Недостатками этих устройств является большое потребление энергии от источников питания и малое быстродействие из-за перезаряда конденсаторов через резисторы схемы.

В предлагаемом разряде динамического регистра сдвига отсутствуют источники постоянного тока и резисторы в цепи перезаряда конденсаторов. Он состоит из двух схем, в каждой из которых конденсатор заряжается через диод от положительного тактового источника питания, а разряжается или через диоды и базу-эмиттер транзистора на отрицательный источник тактового питания, подключенный к эмиттеру транзистора, или через диод схемы

«И» на вход схемы.

Таким образом, питание устройства осуществляется от импульсных источников питания.

Тепловая энергия в резисторе выделяется только во время заряда и разряда конденсаторов. Быстродействие устройства определяется временем перезаряда конденсаторов через прямые сопротивления диодов.

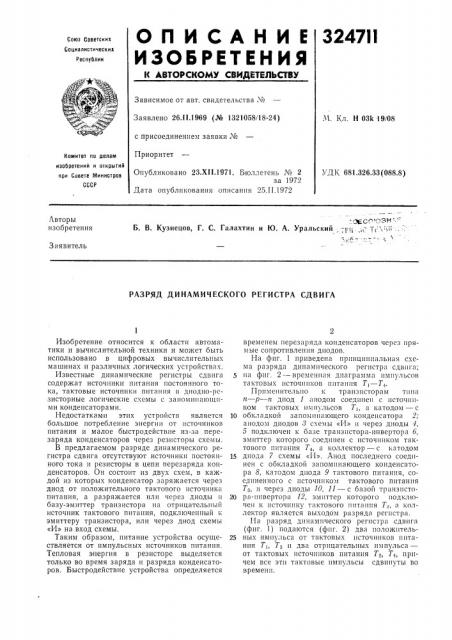

На фиг. 1 приведена принципиальная схема разряда динамического регистра сдвш а; на фиг. 2 — времещтая диаграмма импульсов тактовых источников питания Т,— Т,.

Применительно к транзисторам типа и — р — и диод 1 анодом соединен с источником тактовых импульсов Т,, а катодом — с

lo обкладкой запоминающего конденсатора 2; анодом диодов 8 схемы «И» и через диоды 1, 5 подключен к базе транзистора-инвертора 6, эмнттер которого соединен с источником тактового питания Т4, а коллектор — с катодом

15 диода 7 схемы «И». Анод последнего соединен с обкладкой запоминающего конденсатора 8, катодом диода 9 тактового питания, соединенного с источником тактового питания

Т,, и через диоды 10, 11 — с базой транзнсто20 ра-инвертора 12, эмнттер которого подключен к источнику тактового питания Т>, а коллектор является выходом разряда регистра.

На разряд динамического регистра сдвига (фиг. 1) подаются (фпг. 2) два положнтель25 ных импульса от TBKTQBblx нсточтннсов питания Т,, Тз и два отрицательных импульса— от тактовых источников питания Тв, Т, причем все эти тактовые импульсы сдвинуты во времени.

324711

В. < .Од раз р(lдя рсl IlcTj)

Б указанном регllcTj)c зы лоп(чеc(((Ill (и) ль принимается»(e((b(I ее, я зя логическую единицу — большее зпычсшае напряжения.

Разряд динамического регистра сдвига моi((cT выходи 1 ься В двух состоя пиях.

Тактовый импульс Т! через диод 1 заряжает запоминающий конденсатор 2. После прекращения действия тактового импульса TI заряд на запоминающем конденсаторе изменяется незначительно ввиду малой величины токов утечки закрытых диодов.

Во время действия отрицательного тактового импульсы Т, транзистор предыдущего разряда динамического регистра остается закрытым (логи<(еская единица) и напряжение иа конденсаторе 2 пе изменится, так как ток через диоды 8 отсутствует.

Во время действия положительного тактового импульса Тз заряжается через диод 9 конденсатор 8 и после прекращения действия этого тактового импульса напряжение на копдеисаторе сохраняет свое значение.

Тыктовый импульс Т, поступает на эмиттер транзистора б. Это вызывает разряд конденсатора 2 через диоды 4, 5 и базу-эмиттер транзистора б. Транзистор б открывается.

Конденсатор 8 разряжается через диод 7 коллекторпым током транзистора б.

Далее тактовый импульс Т! заря)кает конденсатор 2. Тактовый импульс Т. не вызывает открывания транзистора 12 ввиду низкого уровня напряжения на конденсаторе 8. Ток через диоды 10, 11 отсутствует.

Таким образом, иа выход передано состояние логической единицы со сдвигом во времени.

Если после действия тактового импульсы TI заряженный конденсатор 2 разрядится пя вход предыдущего разряда во время действия тактового импульса Т, то регистр сдвига бедcT II«»oдитьс(! в состояпии ло(ичсского пуля.

Тактовый импульс Т, зарядит через диод 9 конденсатор 8. Тактовый импульс Т.! конденсатор 8 не разрядит из-за малого напряжения на копдеисаторс 2. Тактовый импульс Т( зарядит конденсатор 2. Тактовый импульс T). разрядит конденсатор 8 через диоды 10, 11 и базу-эмиттер транзистора 12.

Зо

50! j

СДВИГОМ Во ВРЕМЕПИ.

1-!я фпг. 2 приведе«я «рсмсиияя диаграммы работы рсгисгры для слу шя псрсдычп лоп(IССКОГО НУЛЕ(.

Разряд дииамического регистра сдвига мо)кет быть также использован в рязли и!ых лоп(ческих устройства» автоматики и вычислительной техники.

Например, для случая решения лоп(ческой операции «Запрет» A=BC иа «В». 1» (Диоды 8) подается сигнал «С», па «В». 2» (диод 7) подается сипгал «В», аноды диодов 1, 9 соединены с источником положительного тактового питагп(, эмиттер транзистора б соединеи с источником отрицательного тактового питания, а эмиттер транзистора 1 соединен со своим исто шиком отрицательного тактового питания, причем импульсы тактового питания находятся в определенной време«пой зависимости. Таким образом, указа«(юс устройство может быть использовано для построения логически пол пой системы диня»I«Iec«»x элементов.

Предмет изобретения

Разряд динамического регистры сдвига, состоящий из дву» схем, содержащих диод«у(o

:!оп(ческую схему «И», диодпую логическук> схему «ИЛИ»< запоминающий «оидснсатор. транзистор- и иверто р и I (c To 4((I II(II тактового питания, Отли<гаюигиггс<г тем, что, с цел ьн) снижеиия потребляемой мощности и увеличспия быстродействия, в каждой из двух схем запоминающий конденсатор одной обкладкои подсоед(шен к диодиой логической схеме

«И» и через диодпую логическую схему

«ИЛИ» — к базе транзистора-инвертора, при этом в первой схеме запоминающий конденсатор через диод тактового питания подключен к шине первого источника тактового питания, а эмиттср транзистора-инвсртора — к шипе четвертого источника тактового питаlIHH, во второй схеме запоминающий конденсатор через диод тактового питания подключен к шине третьего источника тактового пита(шя, а эмиттер транзистора-ипвертора — к шипе второго источника тактового питания; входами каждой из схем являются катоды диодов логической с»емы «И», а выходом— коллектор транзистора-иивертора.

324711 бык.

Риз г

4зиг 2

Составитель А. Матвеев

Техред Л. Богданова

Корректор Е. Зимина

Редактор Б. Нанкина

Типография, пр. Сапунова, 2

Заказ 304/13 Изд. № 1850 Тираж 448 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4/5