Ячейка памяти на моп-транзисторах

Иллюстрации

Показать всеРеферат

ОЛИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Соввтскив

Социалистическив

Республик Заи симос от авт. сьч.ддстсл; стга ¹ 2778эб

За»влс.то 02.111.19 0 _#_. 1409283/18-24

Ч. Кл. Ст 1Ic 11/40

Комитет i!0 делам

Присритет изобретений и сткрв!тий ири Совете Министров

СССР

УДК 681.327.025 (088.8) Оп,то.л-!. ковано 19.1.1972. Вюллетспь X= 4

Д!In! nod б.,т!кон :!»» o»!!сания 25.I I. 1

Автор из об рот е п и!1

Э. Р. Караханян

Московский институт электронного машиностроения

Заявитель

ЯЧЕЙКА 11АМЯТИ НА МОИ-ТРАНЗИСТОРАХ с пр!тсосдиис;т!тсм за»вки №

Изобретение относится к вычислительной технике.

Известны ячейки памяти на МОП-транзисторах, содержащие запоминающие и нагрузочные транзисторы, между затвором и сто- 5 ком ка кдого иагрузочного транзистора включен конденсатор, Недостатками известной схемы являюгся

on.оситсльио большая величина рассеиваемой мощности и большое время обращения к т0 ячейке.

Предлагаемая ячейка памяти отличается тем, что в нее дополнительно введены транзисторы записи, истоки которых подключены к стокам запоминающих транзисторов, сто- 15 ки — к выходам «О» «1» ячейки, затворы — и шине загшси, и вспомогательные информационные транзисторы, затворы которых подсоединены к затворам информационных транзисторов, стоки — к стокам транзисторов зап;т- 20 си, а истоки — к общей точке схемы.

Это позволяет увеличить быстродействие устройства и уменьшить потребляемую мощность.

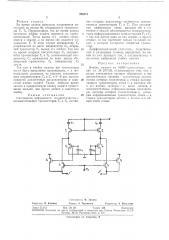

Схема предлагаемой ячейки показана на 25 чертеже.

Ячейка памяти содержит нагрузочные тран.

"-исторы Ti, Тз и запоминающие транзисторы

Т>, Т., соединенные по схеме триггера, вспомогательные информационные транзисторы Т> и 30

Тв, транзисторы записи Т;, Тз и конденсаторы

С! — C;.

Ячейт<т! памяти работает в режимах хранения, записи и считывания.

Режим хранения.

Транзисторы Т; — Тв закрыты, на вход Ф, подаегс» пер!.одически медлен«о изменяющееся напряж и:е. Предположим, что транзистор

Тз закрыт., а транзистор Т,, открыт. В этом случае конде .ситор Сз разряж ll, а конденсатор С.; заряжен. Когда транзистор Тз закрыт, ко!!денсаrop С; медлсшто разряжается током обратно смещеш:ых р переходов, образованных истсковыми ооласт»ми транзисторов Тт, Т; и стоковой областью транзистора Тз с подложкой.

Перподи еское открывание транзистора Т! создает цепь под:аряда конденсатора С, вход

Фт, коидснса,ор С, транзистор Т,, конденсатор С:, земля. Одновременно открывается транзистор T . Однако конденсатор Сз зарядиться не может, так как он зашунтирован открытым транзистором Т».

Таким образом, периодически медленно изменяющееся напряжение на входе Ф! дает возможность поддерживать заряд конденсатора С на необходимом уровне, а так как отсутствует делитель сопротивлений, подключенный к источнику питания, то отсутствует связанное с ним рассеяние энергии, 326641

Составитель M. Зимина

Техред 3. Тараиенко

Редактор Л. Утехина

Корректор А. Вас!!льева

Заказ 513)12 Изд. № 107 . Тираж 448 Подписное

LIHIIIIHII Комитета по делам изобретений и открытий при Совете М!шистров СССР

Москва, Ж-35, Раушская наб., д. 4 /5

Типография, пр. Сапунова, 2

Режим записи.

Во время записи импульсы напряжеьп!я поступают на входы Фз, открываются транзисторы Т-„Та. Предположим, что во время записи состояние ячейки памяти меняется на противоположное. Тогда выход «1» ячейки соединяется с землей, а на выход «О» подается напряжение Е. В этом случае конденсатор Ci, разряжается по цепи: конденсатор С4, открытый транзистор Т;, выход «1» ячеики. Так как

pо время разряда конденсатора С.„закрываются транзисторы Т; и Тв, запоминающий ко !денсатор Сз заряжается по цепи: выход «О», открытый транзистор Та, конденсатор С„ зе. !ля.

Так как В яче!!Ке памяти Все т!па из!!сторы могут быть выполнены одинаковыми, т. е. минимальных размеров, то емкости запоминающих конденсаторов С3 и С„в 6 — 8 раз меньше емкостей аналогичных конденсаторов в известной ячейке памяти. Таким ооразом время записи в предлагаемую ячейку памяти существенно меньше, чем время записи в известную ячей!к .

Режим считывания

Считывание информации осуществляется с вспомогательных транзисторов Т; и Та, состояние которых аналогичны состояни",„ì запоминающих транзисторов Тз и T.. При считывании информации связь выходов «О» и «1» ячейки с землей обеспечивается вспомогательиьи!и информационными транзисторами Т; и Те, и так как всегда один из них закрыт, а другой открыт, то ток протекает только по однон л-1нии, г, которой находится открыпгый транзистор.

10 Дифференциальный усилитель, подключенный к разрядным линиям, определяет, по какой из HIIx проходит ток, а слсдовательно, и состояние выбранной ячейк;! памяти.

Предмет изобретения

Ячейка памяти на МОП-транзисторах по авт. св. М 277856, отл!!ча;оща.чсл тем, что, с целью уменьшения времени обращения, в нее дополнительно введены транзисторы записи, 20 истоки которых подключены к стокам запоминаюгцих транзисторов, стоки — к выходам «О» и «1» ячейки, затворы — к шине записи, и вспомогательные информационные транзисторы, затворы которых подсоединены к затво25 рам информационных транзисторов, стоки — к стокам транзисторов записи, а истокrl — к оощей точке схемы.