Устройство передачи данных1^ ::ciwok>&3hah ^м ' •^-•- ^'-'^'•;ш";^г:г!;^ if;'.-:--' • ^--...--.-, • i

Иллюстрации

Показать всеРеферат

3276I9

Союз Ссветсккз

Социалистические

Ресоублик

ОП ИСАНИ Е

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №вЂ”

Заявлено 27. I I 1.1970 (№ 1417645/26-9) с л рисоеди нением заявки №вЂ” Прнор итет—

Опубликовано 26.I 1972. Бюллетень № 5

Дата опубликования описания ЗО.III.I972

М.Кл. Н 04b 3/04

Коюитет оо делаю оеооретеиий и открытий ари Совете й1ииистрое

СССР

УДК 621.395.4 (088.8) А.втор изобретения

Р. T. Сафаров

Заявитель

А

УСТРОИСТВО ПЕРЕДАЧИ ДАННЫХ

Изобретение относится к области передачн оипналов и может быть использовано в систеМВх связи и телеметрии.

Известно устройсгво передачн данных, содержащее анализатор сигнала, два,за поминающих устройства, блок ве нтилей,и синхронизатор. Это устройство позволяет обрабатывать многоканальное сообщение, исключая из него отсчеты избыточных, каналов. Известные устройства и,меют пустые интервалы между по рциями отсчетов.

Целью .изобретен ия является обеспечение .равномерной передачи в лин ии связи информации, прошедшей об работку, сокращения избыточности .и .грулпирован ия существенных отсчетов пер вой пруппы параметров, подвергну-. тых обработке в:блоках с одинаковым ко IIHBPством отсчетов.

Досгигается это тем, чго образующиеся пустые и нтервалы заполняются информацией, кото рую выдает циклопически работающее второе кодирующее устройство. Для этого к трем выходам синх1ронизато ра подключены соотве1тственно два кодярующих блока для двух групп параметров и коммутатор считывания.,Причем .к,первому выходу си нхронизато ра параллельно:подключены первый нодирующий блок и блок сокращения избыточности, второй вход которого соединен с выходом первого кодирующего блока, а,выход — с коммутатором записи н через линию задержки со вторым входом первого,кодирующего блока. В горой выход этого кадирующего блока связан со вторым входом коммутатора записи, один вы од кото5,рого присоединен ко входу коммутатора счнтывани:я, а остальные, число которых,рав но значносги записываемого кода, — но входам запоминающего узла, .выход последнего,подключен ко входу выходного блока. Вторые IÂõo1о ды запохоинающего узла по числу разрядов считываемого кода связанны с выходами коммутатора считывания, один вход.и один выход которого соедннены со вторым кодирующим блоком, другой вход — со вторым выходом

15 синхронизатора, а другой выход — с выходным блоком, третий выход синхронизатора связан со.вго1рым,входом второго кодирующего блока, второй выход которого подключен к выходно.му блоку.

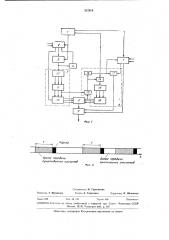

20 На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 показано распре,деление двух групп отсчетов.

Устройство содержит синхронизатор 1, первый кодирующий блок 2, блок 3 сокращения

25 избыточности, линию 4 задержки, коммутатор 5 запиои, запоминающий узел б, второй кодирующий блок 7, коммутатор 8 считывания, выходной блок 9, регисгр 10, матрицу 11, блок 12 ключевых элементов, триггер И, вензо тиль 14, регистр 15, матрицу 1б, формирова327619 тель 17 маркера и дифф ренцирующую цепь 18.

Устройство работает следующим образом.

Синхронизатор 1 управляет, работой основ,ных олоков, выдавая тактовые (опросные) и считывающие импульсы. Кодирующий блок 2 циклически формирует кодовые комбинации, отображающие значения отсчетов па раметров пер вой группы, которые проходят обработку в блоке сокращения избыточности.

Он выдает импульсы, соотвегствующис наличию существенных отсчетов, которые поступают,на вход коммутатора записи, а через линию задержки на вход кодирующего блока 2 для считывания, кодовой комбинации и адреса существенного отсчета. Регистр 10, матр ица 11 и блок 12 ключевых элементов управляют поочередным заполнением ячеек памяти запоминающего узла 6.

При появлении кодовой комбинации, .поступающей на вход последней ячейки запом инающего узла, сраоатывает триггер 13, открывая вентиль 14, через который на,вход регистра 15 подаются считывающие импульсы от синхронизатора. Формируемые на выходах матрицы 1б сигналы считывают показания ячеек запоминающего узла, начиная с первой. При появлении импульса на выходе последней шины матрицы 1б триггер 18 возвращается в исходное состояние. Скачок потенциала плеча тр иггера ди фференцируется и подает сигнал о фор.ми ровании маркера и начале передач и второй группы параметров. Формирователь 17 маркера выдает сигнал о:номере канала, с которого .начинается передача второй группы парамет,ров. После заполнения запоминающего узла срабатывает триггер 18, и скачок его потенциала через дифференцирующую цепь 18 ïîдается на вход второго кодирующего блока 7, из вещая об окончании передачи второй группы параметров.

На фиг. 2 показано,распределение двух групп отсчетов, где интервал времени T для передачи существенных данных, снимаемых с полностью заполненного запоминающего узла, остается неизмвнным. Интервал времени между ними является переменным, он заполняется отсчетами па раметров,,не прошедших обра5 ботку.

Предмет изобретения

l0 Устройспво передачи данных, содержаще синхронизатор, два кодирующих блока:и блок сокращения избыточности, отличающееся тем. что, с целью равномерной передачи ь линию связи .иноформации, прошедшей ооработку, сокращения из быточности:и группирования существенных отсчетов пе рвой группы параметров, подвергнутой обработке, в блоках с одинаковым кол|ичеетвом отсчетов, к трем выходам синхронизагора подключены соответствен20 но два кодирующих блока для двух Прупп парамет ров и |коммутатор считывания, причем к первому .выходу синхронизатора параллельно подключены кодирующий блок и блок сокращения избыточности, второй вход которого

25 соединен с выходом кодирующего олока, а выход — с коммутатором записи и через линию задержки со вторым входом кодирующего блока; второй выход этого блока,связан со вторым входом, коммутатора записи, один вы30 хбд которого присоединен ко входу коммутатора считывания, а остальные, число, которых равно значности записываемого кода,— ко,входам запом инающего узла, .выход которого подключен .ко входу выходного блока; вторые

35 входы запоминающего узла по числу разрядов считываемого кода связаны с выходами коммутатора считывания, один вход:и один выход которого соединены со вторым кодирующим блоком, другой вход — со .вторым выходом 0 синхронизатора, а другой, выход — с выходным блоком; трет ий выход синхронизатора связал со вторым входом второго кодирующего блока, второй выход которого подключен к выходному блоку.

327619

Составитель Н. Герасимова

Текред 3. Тараненко Корректор Н. Шевченко

Редактор Т. Юрчикова

Подписное

Тираж 448

Изд. ¹ l38

Заказ 932

LIHHHHH Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Рауыская наб., д. 4/5

Областная типопрафия Костромского управления по печати

8ремя передачи сущестденных атсчетеВ

Время передачи циклических отс четсб

Фиг. Я