Устройство для получения псевдочастного

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

Сова Соеетских

Социалистических

Республик

Зависимое от авт. свидетельства №вЂ”

Заявлено 25.Y.1970 (№ 1441849/18-24) с присоединением заявки №вЂ”

Приоритет—

Опубликовано 24.11.1972. Бюллетень № 8

Дата опубликования описания 24.IV.1872

М. Кл. 6 06f 7i38 комитет по делам изобретений и открытий при Совете Министрое

СССР

УДК 681.325.5(088.8) Автор изобретения

Л. М. Метрик и Б. И. Рувинский

Заявитель

УСТРОЙСТВО ДЛЯ ПОЛУЧЕНИЯ ПСЕВДОЧАСТНОГО

Изобретение относится к области вычислительной техники и может найти применение при аппаратном вычислении элементарных функций в цифровых вычислительных машинах с плавающей запятой, Известно устройство для получения псевдочастного при вычислении элементарной функции arctgx, содержащее регистры, сумматор и счетчик.

Недостатком такого устройства является низкая точность вычисления функции arctg x.

С ростом модуля отрицательного порядка аргумента элементарной функции arctg х псевдочастное получается денормализованным, а количество нулей в старших разрядах равно модулю порядка.

Целью изобретения является устранение указанного недостатка, т. е. получение псевдочастного сразу в нормализованном виде без увеличения разрядности операционных регистров.

Поставленная цель достигается введением в схему счетчика сдвигов модификатора для получения псевдочастного. В случае положительного порядка аргумента выполняется обратное псевдоделение и получается нормализованное псевдочастное для дополнительного !

1 до значения элементарной функции

arctgx, т. е. этот случай сводится к случаю отрицательного порядка.

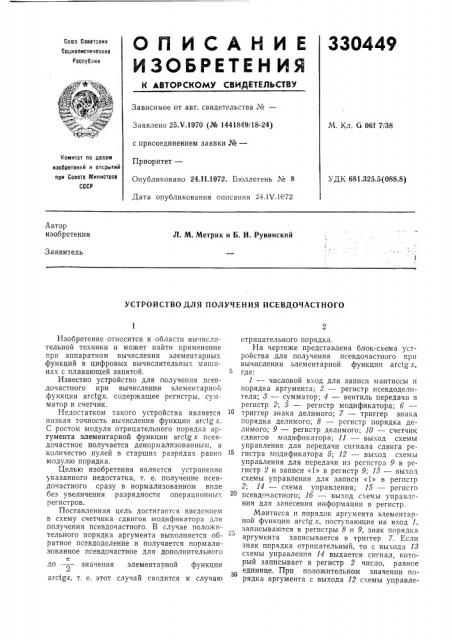

На чертеже представлена блок-схема устройства для получения псевдочастного прп вычислении элементарной функции arctg x, где:

1 — числовой вход для записи мантиссы и порядка аргумента; 2 — регистр псевдоделителя; 8 — сумматор; 4 — вентиль передачи в регистр 2; 5 — регистр модификатора; б—

10 триггер знака делимого; 7 — триггер знака порядка делимого; 8 — регистр порядка делимого; 9 — регистр делимого; 10 — счетчик сдвигов модификатора; 11 — выход схемы управления для передачи сигнала сдвига регистра модификатора 5; 12 — выход схемы управления для передачи из регистра 9 в регистр 2 и записи «1» в регистр 9; 18 — выход схемы управления для записи «1» в регистр

2; 14 — схема управления; 15 — регпсто

20 псевдочастного; lб — выход схемы управл"ния для занесения информации в регистр.

Мантисса и порядок аргумента элементарной функции arctgx, поступающие на вход I, записываются в регистры 8 и 9, знак порядка аргумента записывается в триггер 7. Если знак порядка отрицательный, то с выхода 18 схемы управления 14 выдается сигнал, который записывает в регистр 2 число, равное единице. При положительном значении порядка аргумента с выхода 12 схемы управле330449

Предмет изобретения

Составитель И. Долгушева

Тсхред 3. Тараненко

Корректор T. Бабакина

Редактор В. Нанкина

Заказ 99/568 Изд. ¹ 272 Тираж 448 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред, «Патент» ния И выдается сигнал, который открывает вентиль 4 для передачи информации из регистра 9 в регистр 2 и устанавливает в регистре 9 число, равное единице.

Поскольку порядок делителя принимается равным нулю, то выравнивание порядков, используемое в прототипе, приводит к денормализации и к потере значащих цифр псевдочастного, т. е. к понижению точности.

Для устранения этого недостатка процесс выравнивания запятых исключается введением счетчика 10 сдвигов модификатора, входы которого соединены с выходами регистра порядка 8. Перед началом процесса псевдоделения содержимое регистра порядка о передается в счетчик 10 сдвигов модификатора.

Тем самым разность порядков делимого и делителя учитывается в процессе модификации.

Для осуществления процесса деления выходы регистров 2 и 9 соединяются со входами сумматора 8, выходы которого подаются на входы регистра 9 и триггера 6, запоминающего знак результата на каждом шаге деления. Выход триггера б подается на схему управления 14 и определяет значение сигнала, выдаваемого с выхода lб, соединенного с младшим разрядом регистра 15.

Для осуществления модификации выходы регистра 9 связаны со входами регистра 5, на сдвиговый вход которого подаются сигналы с выхода 11 схемы управления 14. Величина сдвига определяется содержимым счетчика 10, выходы которого соединены со схемой управления 14. Выходы регистра 5 и регистра 2 подсоединены к сумматору 8, выход которого подсоединен к регистру 2 для записи в него модифицированного значения делителя.

1О

Устройство для получения псевдочастпог<> при вычислении элементарной функции

3rctg х, содержащее регистр делимого, регистр псевдоделителя, регистр модификатора, выходы которых соединены со входами сумматора, выходы которого соединены со входами регистра псевдоделителя и регистра

2О делимого, регистр порядка делимого, регистр псевдочастного и схему управления, выходь которой соединены с управляющими входами всех регистров устройства, отличающееся тем, что, с целью повышения точности вычис25 ления функции arctg х, оно дополнительно содержит счетчик сдвигов модификатора, входы которого соединены с выходами регистра порядка делимого, а выходы соединены со входами схемы управления.