Ключевое устройство для перемножения двухвеличин

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 33I485

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сова Советски»

Социалистически»

Республин

Зависимое от авт. свидетельства №

Заявлено 04.II I.1970 (№ 1410496/26-9) с присоединением заявки №

Приоритет

Опубликовано 07.Ill.1972. Бюллетень М 9

Дата опубликования описания 21.IV.1972

М. Кл. Н 03k 17/00

Комитет по делам иаобретений и открытий ври Совете Министров

СССР

УДК 621.374.42 (088.8) I р амайвю®ядов

М. И. Константиновский и Ю. И. Растеряев 1 т с = о- <в ! " t

Авторы изобретения

Заявитель

КЛЮЧЕВОЕ УСТРОЙСТВО ДЛЯ ПЕРЕМНО)КЕНИЯ ДВУХ

ВЕЛИЧИН

Изобретение относится к вычислительной и импульсной технике, а именно к устройствам аналого-цифровых преобразователей.

Известны ключевые схемы, применяемые для осуществления операции перемножения двух величин, одна из которых моделируется напряжением постоянного тока, а другая— относительной длительностью импульса напряжения.

Известные схемы ключей, предназначенные для выполнения операций умножения и преобразования информации, состоят из двух транзисторов и двух соединенных с ними порознь управляющих транзисторов, один из которых включен по схеме с общим эмиттером, другой — с общим коллектором. Входные сигналы, снимаемые с плеч триггера, подаются на базы управляющих транзисторов.

Ключевые транзисторы включены инверсно, благодаря чему достигается минимальное падение напряжения на них в замкнутом состоянии. Выходной сигнал снимается с общей точки ключевых транзисторов, Однако такие устройства характеризуются тем, что в замкнутом состоянии ключа выходное напряжение отличается от опорного из-за наличия нулевого тока управляющего транзистора, включенного по схеме с общим эмиттером; в разомкнутом состоянии уровень напряжения на выходе прп отсутствии входного сигнала (по импульсному входу) не является минимальным из-за наличия нулевого тока транзистора, включенного по схеме с общим коллектором; между управляющими и ключевыми транзисторами отсутствуют формирующие емкости, вследствие чего относительная длительность выходного импульса на высоких частотах может отличаться от входного.

Поскольку управление двумя ключевыми транзисторами производится независимо импульсами положительной и отрицательной

15 полярностей, что при наличии сдвига между ними может наступить положение, когда оба этих транзистора одновременно окажутся открытыми. Это может повлечь за собой выход ключевых транзисторов пз строя. Таким об20 разом, надежность известных устройств недостаточна.

Целью изобретения является создание устройства, которое обеспечивает более высокую точность выполнения операций преобра25 зования и умножения при более высокой надежности действия устройства.

Для этого используется ключевое устройство, включающее усилительный и формирую30 щий каскады, собранные на транзисторах с

331485

55 разными проводимостями и охваченные общей положительной обратной связью.

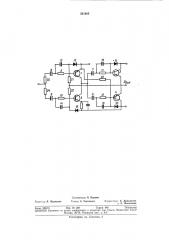

На чертеже приведена схема описываемого устройства.

Принципиальная схема ключа состоит из двух почти идентичных двухтактных каскадов, собранных на транзисторах 1, 2 и 8, 4 с

n — p — и и р — и — р проводимостями. Первый каскад (транзисторы 1 и 2) предназначен в основном для усиления, поступающего с первого (импульсного) входа сигнала по амплитуде без существенного ухудшения фронта импульса, а также повышения входного сопротивления устройства. Благодаря тому, что сигнал с выхода первого каскада поступает на второй формирующий каскад уже усиленным и постоянным по амплитуде, облегчается формирование на выходе второго каскада строго прямоугольного импульса, ограниченного по амплитуде, Коллекторы транзисторов усилйтельного ййскчда..соединены между собой и с оМйРФЙхУДЬФ формирующего каскада. Такое соединение позволяет уменьшить постоянную времени каскада, так как в момент переключения всегда открыт один из транзисторов 1 или 2. Таким путем достигается существенное повышение точности устройства.

Второй каскад (транзисторы 8 и 4) предназначен для точного ограничения амплитуды выходного напряжения по уровню, равному напряжению, поступающему на второй (потенциальный) вход ключевого устройства, Поэтому, если в первом усилительном каскаде транзисторы работают в обычном режиме, то во втором формирующем,— в инверсном режиме. Инверсное включение необходимо для получения наименьшего остаточного напряжения на выходе открытого триода и следовательно меньшей ошибки выходного напряжения по сравнению с входным. B усилительном каскаде уровень напряжения на выходе открытого транзистора не имеет существенного значения, поэтому включение транзисторов здесь обычное.

Двухтактный усилитель в усилительном каскаде применен для точной временной передачи как переднего, так и заднего фронта импульсов, тогда как в формирующем каскаде он необходим для обеспечения равенства амплитуды выходного напряжения входному напряжению. На входах транзисторов как усилительного, так и формирующего каскада установлены разделительные конденсаторы

"— 8, а также сопротивления 9 — 12. Конденсаторы позволяют уменьшить величину входного напряжения, сопротивления же ограничивают ток насыщения и увеличивают входное сопротивление каскадов.

4

Сопротивления 9 — 12 зашунтированы конденсаторами небольшой емкости И вЂ” 1б соответственно, уменьшающими запаздывание фронтов импульса. Параллельно эмиттерным переходам транзисторов 1 и 2 и коллекторным переходам, выполняющим роль эмиттерных переходов транзисторов 8 и 4, установлены диоды. Их роль — предотвращать искажения сигналов по длительности из-за смещения рабочей точки, возникающего вследствие детектирования сигнала на базах транзисторов. Общая точка эмиттеров транзисторов второго каскада соединена через сопротивления 21 и 22 с базами транзисторов первого каскада, Таким образом, все ключевое устройство охвачено положительной обратной связью, уменьшающей погрешность, вызываемую затягиванием фронтов импульсов.

Сопротивление 23 служит для получения нуля выходного сигнала U„„» ïðè отсутствии входного сигнала U, а сопротивления 24 и

25 — для уравнивания крутизны фронтов импульса.

Сочетание в одном ключевом устройстве усилительного и формирующего каскадов, охваченных общей положительной обратной связью, позволило выполнить основные требования, определяющие точность, т. е. повысить входное сопротивление, обеспечить малое запаздывание выходного сигнала, малую длительность фронтов импульса, минимальную разность между входным напряжением постоянного тока и амплитудой выходного импульса, а также малое напряжение при отсутствии сигнала на первом (импульсном) входе.

Устройство сохраняет точность при сравнительно малых амплитудах входных импульсов и благодаря этому хорошо согласуется с устройствами, выполненными на интегральных схемах.

Предмет изобретения

Ключевое устройство для перемножения двух величин, содержащее включенные параллельно транзисторы п — р — п и р — п — р проводимостей, отличающееся тем, что, с целью повышения надежности и точности перемножения, две пары транзисторов, образующие два каскада усиления и формирования импульса, соединены последовательно, причем общая точка двух коллекторов транзисторов первого каскада соединена через развязывающие цепи с базами двух транзисторов второго каскада, а общая точка эмиттеров транзисторов второго каскада соединена через резисторы с базами транзисторов первого каскада, 331485

f5 15/

Редактор Л. Народная

Заказ 903/15 Изд. ¹ 388 Тираж 448 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Составитель Л. Пронин

Техред 3. Тараненко

Корректоры: Е. Давыдкина и А. Николаева