Элемент памяти>&оесоюзн.аяйатшяо-шип'^ен^ биелиотггг =,

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 332563

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалнстииеских

Республик

Зависимое от авт. свидетельства №

Заявлено 25Х.1970 (¹ 1444089/18-24) с присоединением заявки №

Приоритет

Опубликовано 14.IJJ.1972. Бюллетень № 10

Дата опубликования описания 19.IV.1972

М, Кл. Н 031< 3/286

Комитет по делам изобретений и открытий при Совете тЛинистров

СССР

УДК 621.373.544 (088.8) Автор изобретения

К. О. Шепеленко

Научно-исследовательский институт строительного производства

Госстроя Украинской CCP

Заявитель

ЭЛЕМЕНТ ПАМЯТИ

Изобретение относится,к области автоматики и вычислительной техники и предназначено для построения запоминающих устройств дискретной информации, например оперативной информации в автоматизированных системах у правления строительным производством.

Известные элементы;памяти, например триггеры, связанные логические элементы ти па стрелки Пирса («ИЛИ вЂ” HE») и другие, содержат транзисторные каскады, связанные глубокой .положительной обратной связью (выход одного ка скада соединен со входом другого, а вход — с выходом.

Недостатком известных элементов является то, что на один элемент памяти расходуется несколько транзисторов с резисторами, конденсаторами, диодами. При большом числе ячеек памяти запоминающее устройство, построенное из таких элементов, получается довольно сложным и дорогим. Кроме того, .в известных пороговых потенциальных элементах памяти для обеспечения строго определенного состояния элемента после включения питающих напряжений требуется специальный сигнал (установка в «нуль»), что приводит,к дополнительному усложнению устройства.

Цель изобретения — упрощение конструкции пороговых элементов памяти, снижение их стоимости и исключение необходимости формирования сигнала начальной установки в

«нуль» при включении напряжений, Эта цель достигается тем, что предлагаемый элемент памяти выполняется на одном тран5 зисторе по схеме с общим эмиттером и нагрузочным резистором в коллекторной цепи, а в базовую цепь транзистора, смещенную в исходном состоянии в прямом на правлении, подаются через запоминающий конденсатор и

10 вентиль тактовые импульсы, обеспечивающие заряд запоминающей емкости, На вентиль через резистор заведено напряжение обратной связи с выхода .потенциального элемента памяти.

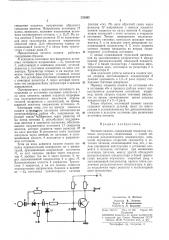

15 Схема предлагаемого транзисторного элемента памяти приведена на чертеже.

В коллекторную,цепь транзистора 1, например, р-и-р типа включен резистор нагрузки 2.

Для смещения базовой цепи транзистора в

20 прямом на правлении в исходном состоянии служит резистор смещения 8, которым обеспечивается режим насыщения транзистора 1.

Для получения режима отсечки коллекторного тока служит запоминающая емкость 4, 25 связанная с одной стороны через вентиль 5 и разделительную емкость б с источником тактовых импульсов 7, а с другой через интегрирующую цепь, состоящую из резистора 8 и конденсатора 9, с базой транзистора l. На анод

30 вентиля 5 через резистор 10 от источника 11 смещения, подается напряжение обратного смещения вентиля. Напряжение источника 11 равно, примерно, половине напряжения источника коллекторного питания, т. е. Е„12. На катод вентиля 5 через резистор 12 из коллекторной це пи транзистора подается на пряжение обратной связи. Для обеспечения заряда запоминающей емкости 4 в обход базы транзистора 1 служит диод И.

Предлагаемый элемечт памяти работает следующим образом.

В исходном состоянии при включении источни ка питающего напряжения — Ен транзистор

1, работающий в ключевом режиме, устанавливается в состояние насыщения по цепи коллектора. Транзистор открыт, и на выходе элемента памяти фиксируется условный сигнал

«0». Это устойчивое состояние поддерживается с помощью резистора 8, через который протекает ток смещения базы транзистора в прямом на правлении.

Одновременно с включением питающего напряжения от источника тактовых импульсов 7 на вход элемента памяти подается непрерывная последовательность импульсов отрицательной полярности с амплитудой, не превышающей величину напряжения источника 11.

Благодаря.. тому,;что на выходе,элеменга памяти вггисходном состоянии автоматически устанавлйвается.сигнал «О», напряжение обратной связи:,:"йодаваемое через резистор 12 на катод вентиля 5, способствует поддержанию вентиля в закрытом состоянии, обеспечиваемом напряжением источника 11 смещения вентиля, которое .подается через резистор 10 на анод вентиля. В результате этого тактовые импульсы через вентиль не проходят, и запоминающая емкость 4 находится в разряженном состоянии.

Если на вход элемента памяти подать импульс отрицательной, полярности, но с амплитудой, превышающей напряжение источника

11, то этот импульс, пройдя через конденсатор 6, пройдет так же и через вентиль 5, через запоминающий конденсатор 4 и диод 18.

Запоминающая емкость 4 зарядится. Транзистор 1 закроется, и на его выходе появится отрицательное напряжение, близкое к величине — Е, источника коллекторного питания

332563

4 (сигнал «1»). По цепи обратной связи через резистор 12 напряжение с выхода элемента памяти подается на катод вентиля 5, поддерживая последний с этого момента в открытом

5 состоянии, Теперь непрерывная последовательность тактовых импульсов проходит через вентиль 5, и на каждом такте дозаряжает запоминающий конденсатор 4. С этого момента элемент памяти находится во втором («еди10 ничном») устойчивом состоянии.

С целью сглаживания пульсаций напряжения на запоминающем конденсаторе 4 между ,правой (положительной) обкладкой конденсатора 4 и базой транзистора 1 включена инте15 грирующая цепь, состоящая из резистора 8 и конденсатора 9.

Для надежной работы элемента памяти время разряда запоминающего конденсатора 4 должно превышать в 1,5 — 2 раза период сле20 дования тактовых им пульсов.

Перевод элемента, памяти из состояния «1» в состояние «0» в процессе работы может осуществляться различными способами, например, путем запрета подачи тактовых импуль25 сов на время, .превышающее время разряда конденсатора 4 в 2 — 3 раза.

Таким образом, настоящий элемент памяти содержит минимум деталей, .прост по конструкции и устанавливается без дополнительных

З0 сигналов в исходное состояние,при включении источника питания.

Предмет изобретения

Элемент. памяти, содержащий генератор тактовых импульсов, соединенный с одной обкладкой разделительного конденсатора, ключевой нормально открытый транзистор и ис40 точник питания, отличающийся тем, что, с целью упрощения конструкции и установки элемента в исходное состояние при включении источника питания, между другой обкладкой разделительного конденсатора и базой транзи45 стора введены нормально закрытый диод и запоминающий конденсатор, причем точка соединения разделительного конденсатора и диода .подключена через резистор к коллекторной цепи транзистора, Составитель А. Матвеев

Редактор В. Левятов

Техред А. Камышникова

Корректор Л. Царькова

Заказ 1011/17 Изд. М 359 Тираж 418

Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 475

Типография, пр. Сапунова, 2