Устройство для автоматической регистрации

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республин

ОПИСАНИЕ

ИЗОЫ ЕтЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зяв ic;».oe or авт. свидетельства Л"-Заявлено 02.Ч1,1970 (№ 1442222/18-10) с прпсоедипгпц3ем заявки № -—

G 0! г 19/12

|томитет ло делам изобретений и открытиЯ ври Совете Министров

СССР

П13пор11тст—

Опуб.7иковяно 21.1V.1972. Бюл7етснь <¹ 14

621.317.725 (088.8), 1,ятя опублпко13янпя описания 17.Х.1972 и|С . СС1ОЗ! 11

, I

P. А. Зуев, Э. С. Каташков, И. Ф, Коньков и A. П. Пахомов

Авторы изобретения

Всесоюзный научно-исследовательский и конструкторский институт научного приборостроения

3 я я витель

УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОИ" РЕГИСТРАЦИИ

СРЕДНЕИ СКОРОСТИ МЕДЛЕННО ИЗМЕНЯЮЩИХСЯ

НАПРЯЖЕН И Й

Изобрстенпс относится к области приборостроительной техники.

Известны устройства для автоматической регистрации средней скорости медленно изменяющихся .напряжений, содержащие последовательно включенные компенсатор, преобразоватсль измеряемого сигнала;,вычислительный блок, регистрирующее устройство 11 блок упра 13ления.

Предлагаемое устройство отличается от известных тем, что оно снабжено тремя упразляемыми переключателями и двумя регистрами, выход первого .из которых соедине:| со,в«одом комненсатора, и через первый управляемый переключ атель со входом вычислительного блока, выход второго регистра соединен через первый управляемый псрсключатель со входом вычислительного блока и через второй управляемый,переключатель со входом первого .регистра, выход вычислительного блока через третий упра вляемый переключатель соединен с регистрирующим устройством и входом второго регистра, а выходы блока управления подкл|очены ко входам управляемых переключателей и обоих регистров. 25

3TIl Отличия 1103130.7ßIoò IIOBhlcHI ь стабн7ьность и чувспвительность устройства.

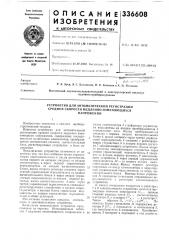

Ьлок-схема описываемого устройства представлена на чертеже. Испытываемый источник 1 медленно изменяющегося напряжения и зо выход компенсатора 2 с цифровым упраьленисм подключены ко входам .преобразователя 8

«напряжение — код». Выход преобразователя соединен с первым входом вычислительного олока 4, выход которого через третий управляемый переключатель 5 соединен с регистриру1Ощим устройством 6.и входом второго регистра 7 запоминающего устройства. Ьыход второIo регистра запоминающего устройства через

«торой управляемый переключатель 8 соединен со входом первого регистра 9 запоминающего устройства и через первый управляемый перск,початель 10 — со вторым в«одом вычислительного блока. Выход первого регистра

:|одк,7IO Ieli iKO 13«07 |компенсатора 11 1ерез первый управляемый переключатель ко входу зычислптельного блока. Выходы блока управления 11 соединены со в«одари управляемы«переключателей Il регистров запоминающего у c Tp О||яств а.

К началу очеред.|ого измерения в репистрях

7 н 9.запоми 1а|ощего устройсэва «рапится предыдущее значение напряжения U» .! причем старшие разряды числа U » I располагаются в регистре 9, а младшис U"». — в регисгре 7.

Таким образом U» i =- U, !+О"„!. По команде блока управления 11 содержимое регистра 9 (U !) передается в компепсатор 2, где преобразуется в напряжение. Преобразователь 3 измеряет и перево!дит в код разность

336608 выходных напряжений испытываемого источника 1 и компенсатора 2 U„— U » 1. Эта разность напряжений подается на первый вход вычислительного блока 4, на второй вход которого через первый управляемый переключатель 10 подается содержимое регистра 7. Вы5 числительный блок 4 совершает операцию вычисления полной разности напряжений: (л — 7 п-1) — (1" п 1 — — - 1л (1 л 1+ " и- I)

Результат операции через третий управляемый переключатель 5 по команде блока управления 11 вы водится на регистрирующее устройство 6. Для запоминания нового значения напряжения У„на вгорой вход вычисл ительного блока 4 по команде блока управления П через первый управляемый переключатель 10 поступает содержимое (U j) регистра 9.

Вычислительный блок 4 выполняет операцию вычисления полного значения напряжения U по алгоритму: (Un — 1л-1) U n 1== — " 1 ((кс-! — U ï i) — -У

Результат операции по команде блока управления 11 через третий управляемый переключатель 5 передается в соединенные последовательно с помощью второго у правляемого переключателя 8 регистры 7 и 9 запоминающе- 30 го устройства. На этом цикл заканчивается.

Измеренная разность зафиксирована регист рируюп им устройством 6, в регистрах 7 и 9 запоминающего устройсгва хранит я новое значение напряжения. 35

Положительный эффект, достигаемый при применении данного устройства, основан на использовании кратковременной (между двумя соседними измерениями) стабильности опорных источников. 40

Это объясняется тем, что с помощью преобразователя «íапряжение — код» и вычислительного блока 4 автоматически производится корректиронка значения выходного напряжен|ия компенсатора 2,перед каждым циклом опредс- 43 ленпя стабильности. Так как длительная cIабильность делителя коипенсатора 2 имеет oo, ее высокое значение, чем длительная стабильность опорного источника компенса тора 2, цифровой эквивалент выходного напряжения компенсатора 2 может сохраняться неограниченно долго без погрешностей хранения. При суммировании предыдущего значения напряжения на выходе компенсатора 2, хранимого в регистрах 7 и 9, со значением малой разности приращения напряжения величина напряжения компенсации корректируется:в начале следующего цикла измерений до значения, определяемого в основном стабильностью о порного источника компенсатора за время, прошедшее от предыдущего замера.

Применение данного усвройства позволяет припци пиально приблизить точносгь измерения средней скорости медленно изменяющихся напряжений к кратковременной стабильности опорных источников.

Пережмет изобретения

Устройство для а|втоматической регистрации средней скорости медленно изменяющихся напряжений, содержащее последовательно включенные компенсатор, преобразователь измеряемого сигнала, вычислительный блок, регистрирующее устройство и блок управления, отличающееся тем, что, с целью повышения стабильности и чувствительности устройства, оно снабжено тремя управляемыми переключателями и двумя регистрами, выход первого из которых соединен со входом компенсатора и через первый управляемый переключатель со входом вычислительного блока, выход второго регистра соединен через первый управляемый переключатель со входом вычислительного блока и через второй управляемый переключатель со входом первого регистра, выход вычислительного блока через третий управляемый переключатель соединен с регистрирующим устройством и входом второго регистра, а выходы блока управления подключены ко входам управляемых переключателей и обоих регистров.

Состав пель В. Скоморохов

Тсхред Л, Богданова

Корректор Е. Миронова

Редактор С. Хейфиц

Областная тиисграф.iÿ Ко=тротлского у:I",.авле:н;я о и !;iти

Заказ 3041 Изд. ¹ 537 Тираж 448 11одплсно

ЦНИ11ПИ Когянтста во дедагя изобретений я открытий прн Совете Министров СССР

Москва, Ж-35, 1 аушская иаб., д. 4,. 5