Схема совпадения

Иллюстрации

Показать всеРеферат

Сс!сз GOBcici(llx

Свдиалистическиз

Республие

Зягвнспмое от авт. свидетсльства №вЂ”.Ч.1,.!. Н 03k 19/24

Зяявс!сно 29.711.1970 (№ 1471808/26-9) с !Грисооду!Некием заявки №вЂ”

Ко!лите! по делам изобретений и открытий при Совете министров

СССР

11р!1Орнтст—

УД1 681.3.056 (088.8) Оп блпковано 21.1V.1972. Вюллстсш М 14

Дятя о!!убл!!конг!!!ия описан!!я ЗО.Х.1972

Авторы изобретения

И. И. Епик и Б. И. Прокофьев

3 я я витель

СХЕМА СОВПАДЕНИЯ

° т

Изобретение относ11Гея к области радиотехники и может быть использовано в устройствах автоконтроля и управления, а также в дсшифрующих устройствах.

11звестна схема совпадения, содержащая запоминающие ячейки, каждая пз которых

В1>!ПОЛ г!ЕНЯ 1l3 1 Л10г!ЕВОЪ! Э 1ЕМЕг!ТЕ, НЯПРИМЕР

ДИНИСГОРС.

В известном устройстве сигна l на выходе появляется лишь при наличии управляюпГих поздействи1! одновременно па всех входах илн с приходом .последнего воздействия, когда все входные сигналы разнесены во времени.

Цель изобретения — Гвыдача сигнала одновременно с последним запоминанием, входного воздействия при случайном его изменении во времени и использование общего для нагрузки п запоминающих ячеек источника пчтяния.

Достигается это тем, что катод ключевого элемента предыдущей ячейки через разделительный диод в проводящем направлении подкл1очен к аноду ключевого элемента последу!Ощей ячейки. Для использования общего для нагруз1си и запоминающих ячеек источниКаг ПИТЯНИЯ 1 1 ЯТОДЯМ .КЛ10ЧЕВЬ!Х ЭЛЕМЕ1П ОВ всех ячеек (кроме:последней) подключены,резисторы, а в последней ячейке резистор подключен к аноду ключевого элемента.

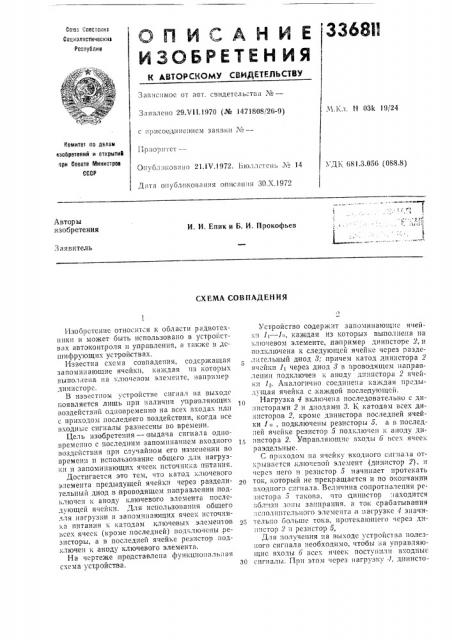

На чертеже:предста влена функГГиопаль:!ая схема устройства.

Устройство содержит запоминающие ячейки 1! — 1., каж!дая из которы выполнена на клю-.евом элементе, на пример динпсторе 2, и подкл1очена к следующей ячейке через разделительный диод 8; причем катод динистора 2 ячейки 1! через диод 8 в проводящем Н311раеле ии подключен к аноду дннпстора 2 ячейКll 1Е. ЛНЯЛОГпг1НО COPÄHHPH3 КаждаЯ ПpP;IÅ>1пущая ячейка с,каждой последующей.

Нагрузка 4 включена последовательно с дпнпсторами 2 и дс!Одами 3. К катодам всех ди11псторов 2, кроме динистора последней ячейки 1 и, подкл1очен1>1 резисторь! 5, а в последнei ячейке резлстор 5 подключен к аз!оду динистора 2. У правля!Оп!не входы 6 всех ячеек раэдельные.

С ПРИХОДОМ На ЯЧЕЙКУ ВХОДНОГО С>и па 13 Открьп1ается,ключевой элемент (чинистор 2), и через него и резистор 5 начинает протекать

gg ToK, которыЙ не прекращается и по 01<ончянии входного сигналя. Величина сопрот11вления pe:;Hcrop3 5 т11ковя, что !динистор:!аходится нбл.тзп зоны запирания. а ток срабатывания исполнительного элемента B нагрузке 4 зна !н25 тельно больше тока, протекающего через дннпстор 2 и резистор 5, Для получения на выходе устройства полезного сигнала необходимо, чтобы на управляющие Bxoëû 6 всеx. ячеек поступплн входные

30 сигналы. Прн этом через нагрузку -Г, дннисто336811

1г

Состаз»гс Ib Л. Багян

Текрод Л. Богданова

Редакгор Л. Мазуроиок

Корректор О, Волкова

Заказ 3049 Изд. Ао 548 Тираж 44ь Поггвиснос

ЦНИИПИ Ком:rrera но дела»и»зобрстезий» открытий н и Созете !ии»стров ССС(Москва, K-36, Раушскзя»аб., д. 4/5

Обл. т»». 1 острогаского у»равлення издатезвств, »олнгр»рин» книжной торговли ры 2 и диоды 8 ..потечет ток, достаточный для срабатывания исполнительного элеме !та в нагрузке 4.

Таким образом, сигнал выдается одновременно с запоминанием входного воздействия при случайном его изменении во времени.

Предмет изобретения

1. Схема совпадения, содержащая запоминающие ячейки, каждая из которых выполнена на ключевом элементе, например, динисторе, отличающаяся тем, что, с целью выдачи сигнала одновременно с последним 3апоминанием входюго воздействия при случайном его изменении во времени, катод ключевого элемента предыдущей ячейки через разделительный диод в проводящем направлении подключен к аноду ключевого элемента последующей ячейки, 2. Схема совпадения по и. 1, отличающаяся тем, что, с целью использования общего для нагрузки и запоминающих ячеек источника

10 питания, к катодам ключевых элементов всех ячеек, кроме последней, подключены резисторы, в последней ячейке резистор, подключен к аноду ключевого элемента.