Многоканальный цифровой коррелятор

Иллюстрации

Показать всеРеферат

337784

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

М АВТОРСИ)МУ СВИДБ ЕЛЬСТВУ

Слито Саветскит

Социалисти !еских

Республик, аФ" . ф фЯф - -гг у

Зав !симов от авт. сьидетельства №

Заявлено 07.Х.1970 (№ 1490059!18-24) М. Кл. G 06(15, 34 с присоединением заявки №

Комитет по делам

Приоритет

Опубликовано 05.V.1972. Бюллетень ¹ 15

Дата опубликования описания 26Х.1972 изобретений и открытий при Совете Министров

СССР

УДК 681.325,36(088.8) 11,1 - » - - "> ">"; y ! с > >»)> ц q »

°, -. !>»

Авторы изобретения

Г. Я. Бахчиев и Э. А. Саакян

Заявитель Тбилисский филиал Всесотозного научно-исследовательского института метрологии им. Д. И. Менделеева

МНОГОКАНАЛЬНЬ! Й ЦИФРОВОЙ КОРРЕЛЯТОР

N — 1 ",, (!Т,) = — », х()гТ,)х()гТ, — Ò,) в=о

Изобретение относится к технике статистических измерений случайных процессов.

Предлагаемый многоканальный цифровой коррелятор предназначен для вычисления оценок корреляционной и взаимокорреляционной функции реализаций центрированных станционарных на интервале наблюдения процессов в соответствии с алгоритмами

1 !» — r

К (iТо) — $ Х()гТо)1()гТо гТо)> =о где Л вЂ” об ьем выборки; !Тс — интервал задержки; !. =-- 1 —: tl, !7 — 1псло а !1 71Л!131!!туе!>>!1>1х 1 о1 чек; T = — — и fp — частота квантования вход.)о о ных сигналов x(t) и )!(t) х(ЬТ,), у(lгТ,), хфТ, — iT,); )у(1гТ, — iT,) — дискреты реализаций центрированных проо цессов х(/) и g(t) в моменты времени )г,Тр и

)гТо — 1Т..

Известные корреляторы отличаются громоздкостью оборудования, сложностью конструктивных связей узлов, невысокой степенью унификации узлов и взаимозаменяемости блоков. Последние обстоятельства значительно снижают коэффициент готовности устройства и стало быть уменьшают надежность аппаратуры в целом. Кроме того, устройству свой5 ственно низкое быстродействие.

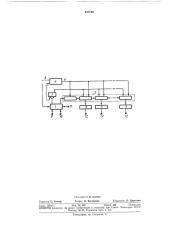

На чертеже приведена блок-схема предлагаемого цифрового многоканального коррелятора.

Устройство содержит двухканальный вре10 мя-импульсный преобразователь типа аналогкод 1, последовательно подключенный (и+1) -каскадный регистр сдвига 2, триггер У, синхронизатор 4 и и накопителей 5. Каждый каскад регистра 2 состоит из m+2 раз15 рядов. Накопители 5 состоят из последовательно подключенных m+2 разрядного накапливающего сумматора со сквозным переносом и (/ †) разрядного двоичного счетчика (l выбирается из условия N=27), причем

20 входы т+2 младших разрядов накопителей

5 связаны с соответствующими выходами п ря мого кода регистров 2. Каждый накопитель 5 снабжен триггером знака, единичным выходом связанным Ic входом младшего раз25 ряда накопителя (указанные триггеры и их соответствующие связи на чертеже не отражены). Правый информапионный выход преобразователя 1 подкл1очен ко входу второго разряда первого 7 аскада регистра 2, а левый

30 информационный выход — к счетному входу

337784 триггера 8, единичный выход которого связан с шиной опроса регистра 2, кроме первого каскада. Выход 6 синхронизатора 4 подключен к шине сдвига регистра 2, а выходы 7 и о связаны соответственно с входом установки нуля триггера 8 и с управляющим входом преобразователя 1. В регистре 2 сдвиг двоич. ного кода осуществляется в правую сторону младшим разрядом. Первый (левый) каскад регистра 2 кроме сдвига кода должен осуществлять также преобразование числа, представленного в унитарном коде (последовательностью импульсов), в двоичный код.

На входные клеммы 9 и 10, являющиеся информационными входами преооразователя 1, соответственно подаются входные процессы

C х() и у(1), а на входную клемму 11 подается смещение +Е,.„, равное максимальной отрицательной амплитуде входных сигналов.

m+l выходных клемм 12 каждого накопителя соответственно подключены к выходам прямого кода накопителей 5.

В исходном состоянии Ь(п+1) каскадах регистра 2 зафиксирован код нуля, триггер 8 находится в нулевом положении, в каждом из п накопителей 5 зафиксирован двоичный код числ и — l> Ес и

В предлагаемом устройстве процесс определения и точек корреляционной функции с.уществляется за X циклов.

С началом первого цикла анализа на выходе 7 синхро 4 появляется импульс, который поступает на управляющий вход преобразователя 1 и дает команду на преобрас о зование сигналов x(t) +E,,„и Jl(t) +E,,„. На правом и левом выходах преобразователя 1 соответственно появляются две последовательности импульсов, число которых в первой последовательности соответствует дискрете о

X(kTo) -+ E„„, Po PT0 QH — H K eTe g(kTo)+

-,, -L,,, Последовательность импульсов, соответствующая дискрете у(1:Т,) +Е„„преобразуется в первом каскаде регистра 2 в двоичный код, а последовательность импульсов, соответствующая дискрете х(И,) +Envoi поступает на счетный вход триггера 8, в результате на единичном выходе триггера появо

x(kTo) + Ес ляются импульсы, производящие кратный опрос и старших каскадов регистра 2. После окончания обеих последовательностей на выходе 6 синхронизатора 4 появляется один импульс, который осуществляет сдвиг кодов во всех каскадах регистра 2 вправо на один разряд. Далее на выходе 7 синхронизатора 4 появляется импульс, производящий установку нуля триггера 8. При

5 этом если число импульсов в последовательо ности, соответствующей ординате x(kT,) +

+Е,,„было нечетным, то на единичном выходе триггера 8 формируется импульс, осущсствляющий дополнительную перепись кодов из и старших каскадов регистра 2 в m+1 младших разрядов соответствующих накопителей 5. Если же число импульсов в последовательности было четным, то дополнительной перезаписи кодов из регистров 2 в накопители не производится.

После установки нуля триггера 8 на выходе

6 синхронизатора 4 появляются т+1 импульсов, которые произведут перезапись кодов

2Q чисел из каждого предыдущего каскада в последующий каскад регистра 2. При этом пер|вый каскад регистра 2 полностью освобождается. На этом завершается цикл работы устройства. Последующий цикл анализа осуществляется в последовательности, описанной выше.

Из описания принципа работы предлагаемого коррелятора видно, что в каждом цикле анализа нет необходимости отводить спе3Q циальное время для производства и умножений. Эти умножения осуществляются автоматически одновременно с процессом преобразования ординат и завершаются с окончанием преобразований.

Предмет изобретения

Многоканальный цифровой коррелятор, содержаший синхронизатор, многокаскадный

4р сдвиговый регистр, накопители, времяимпульсный преобразователь типа аналог-код, первый выход которого подключен ко входу первого каскада сдвигового регистра, а вход — к первому выходу синхронизатора, от45 личающийся тем, что, с целью повышения быстродействия и упрощения устройства, он содержит триггер, счетный вход которого соединен со вторым выходом время-импульсного преобразователя, а единичный выход — с ши5Q ной опроса каскадов, кроме первого, сдвигового регистра, выходы опрашиваемых каскадов подключены ко входам соответствующих накопителей, а сдвиговая шина регистра связана со вторым выходом синхронизатора, 55 третий выход которого соединен с нулевым входом триггера.

337784

9 10

Составитель В. Орлова

Техред Л. Богданова

Корректор Л. Царькова

Редактор Е. Гончар

Типография, пр. Сапунова, 2

Заказ 1548/11 Изд. Мз 689 Тираж 448 Подписное

ЦНИИПИ Комитета пц делам изобретений и открытий при Совете Министров СССР Москва, Я-35, Раушская наб., д. 4/5