Вычислительно логическое устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

337824

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 09.У!11969 (№ 1346082/18-24) с присоединением заявки №

Приоритет

Опубликовано 05Х.1972. Бюллетень № 15

Дата опубликования описания 5ХП.1972

М. Кл. G I I C 15j00

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 681.327.6(088.8) Авторы изобретения

В. Г. Колосов, В. Ф. Мелехин и С. Д. Омаров с,.с " ..;

Ленинградский ордена Ленина политехнический институт им. М. И, Калинина й->тли 41.

Заявитель

ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО

Изобретение от носится к области за поми,на,ющих у.стройст в.

Известно IBbI%HlcJIBTeJIblHo-логическое устройство, содержащее мапнитный оперативный накопитель информации ic:разрядными ши|нами, усилители IBooïðoHçâåäåíHÿ, цодключен ные через соответ ствующие диоды .к регистру регенерации, матрицу магнитных сердечников с прямоу голыиой петлей ги|стерезиса,ППГ, пропьипых взаим но пе|рпендикуляр ньвми адрес н ыми и раз ряд ными шинами, а также первыми н вторыми диагotHBJIьными шинами, два

peBeplcmIBiHbIx,дешифратора, реги|стр с д вигателя. Однако эти устройства имеют сложную ко н стру1кцию,и малую скорость работы.

Описываемое устрой ст во отличается от известного терм, что разрядные ши ны матрицы подключены одни ми конца ми IK IcooTIBeгст вующит входам усилителей:воспроиз веде ния, .адрес ные ши|ны матр|ицы подсоеди не ны к выходам 1регистра сдвигателя, входы которого через соответствующие диоды соединены,с выходами усилителей fBoclIIpoHçâåäåHHÿ, à пе рвые и IBTopbIe диагонал ыные шины матрицы подключены соответственно IK IBыходам перBoI o и второго реверсив ных дешифрато ров.

Указанные, отличия позволяют упростить устройст во и повьвсить его быстродей ст вие.

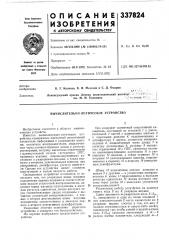

На чертеже изображено предлагае мое устройство.

Оно содержит магнитный оператив ный IHBко питель, состоящий из основной 1 и до полБительной 2 частей. ic разрядными шинами 8 и адресными .шинам|и 4, подключенными к дешифратору 5 адреса, усилители воспроизведе ния 6, подключенные через дио|ды 7 E регистру регенерации 8, матрицу 9 магнитных сердечни|ков 10 с ППГ, прошитых взаимно пер|пе нд1икуля ряыми адресными 11,и разря дными 12 шинами, а также |первыми .18 и вторыми 14 диагональными щи нами, подклто,че н,ными .к перв,ому 15 и,вто,рому 1б ревер сивным дешифраторам.

Ши ны 12 подключены одними ко нцами к шинам 8 и другими — к усилителя м во с произведения 6, шины 11 п1ри|соеди нены к выходам регистра сдвигателя 17, входы которого с вязаны через диоды 18 с выходами усилит елей

20 воспроизведения б.

Рассмотрим работу у стрэй(ства .на при мере сд1ви га ко да Х на К разрядов 1в право.

С двиг двоичного траз ряднопо кода Х:Х...

Хь за пи са нного в од ну из ячеек асио|в|ной 1

25 и1ли,до палнитель ной 2;части,накопителя Ба k разрядов BIIIpBiBo состоит в том, что код Х должен переза писатыся в какую-либо ячейку на|капителя TBIK, что бы самый старший разряд кода Х(Х) оказался за писанным .в т — k

30 раз ряд ячейки накостителя, 1следующий т — 1

337824

10

3 разряд кода Х(Х f) IB m — k — 1 Разряд ячейки и Та!К далее. При этом k младших разрядо в кода Х могут быть отбро ше ны (вытеснены) из,матрицы (rIpoIcToH »сдвиг), либо записаны ra Tv же ячейку,HBKQIIIHTeJIH в разряды ос вободи вшиеоя от старейших р,аз рядо в кода Х (циклический

cpiBmr) .

Опера сия сдвиг кода Х на k ðаз рядо в егираво выполняется за четыре такта.

iB пер вам та кте,код Х, считываемый с какой-ли 60 я чейни основной 1 или допол нителыной 2 части IHBIKo!rlHTeJIя через усилители во с прои з ведения б диодо в 18, записывается ia регистр 1сдви|гателя,17, К козинцу перьвого такта ia реги стуре сдвигателя 17!будут подпото влены те разряды, которым в IKoge Х сîîTiaе1cTtBoiBBJIa единица.

В исходном со стоянии IB!ce сердечни ки мат.рицы 9 находятся в положении;ноль и готовы для п|риема сдвитaeiMoro кода.

Во IBTopoM такте сипналом из устройства управления (на чертеже,не показано) считывается colcTQHHiHe репистра,сд|вигателя 17 и создаются полутоки в адресных шинах 11.

О д новреме н но опраши вает ся реверси в ный деши|фратор 15 в результате чего в k-ой диагональной швне 18 фор мируется полуток. Полутоки в адресных, шинах 11,и в k-,oé диагональной ши не 18 за письпвают сд ви гае мый код

Х |в сердечни ке матрицы |на irreipeicечен и и этих ши,н.

Если « выталкиваемые» k младших ip,азрядов сдвигаемого кода требуется за писать ос вободив шиеся в k старших р азрядов, то одновремВнно )c,äåøèôiðàòîðîiì 15 у стро йством управления опрашивается,де1шиф ратор

1б, который |выдает полуток в k диагональную ши ну 14. Тогда k младших разрядов зали шут ся ia сердечнике матер -rrbr на пересечении k-ой диагоналыной шины 14 и адресных

Ши н 11. (В третье м та кте,зааи сан ный в,предыдущем

TaiKTe в сердечники матрицы код Х считывает ся в perH!crp peireiaeрацни 8.

В .случае простого сд|вига импульсом полного тока считывают|ся только т — k,стар:ших раз рядов кода Х по k-ой диагональной ,шине,18. При этом:в,разрядных ши нах 12 наводится в.д.с., которая через усилители во с произ веде ния б, диоды 7 за писывает код

Х в iperHICTp ре ге|не рации,:начиная ic m — k разряда по 1-ый разряд регистра регенерация 8.

iB случае ци|клического сдвига одновре ме нно перемапничиваются сер|дечни ки k — m диагональными ши нами 18 и 14. .В,режиме циклического сдвига,воз може н случай сдав ига с удвоенной точно стью, который отл|ичает ся от циклического сдвига терм, что k,младших разрядо в сдвинутого кода считывается в любой следующий такт по k-.ой ди а го налыной iIIIHIHe 14.

В четверто м,такте,сдвинутый,код Х записывается в од ну из ячеек,накопителя. Для это го устрой стево у п ра вления о праши вает регист р .регенерация 8, который выдает полутоки в соответст вую цие разрядные шины 12.

Од но време нно в нужную адресную штину 4 выдаемся полуток, который, суммируясь с Illoлутоками разрядных шин 12, запи сьивает сдвинутый код Х в ячейку накопителя.

OIlrepairIHH сдвиг кода Х на k разрядов влево произ водится аналогично описа н ной выше операции сдвига кода Iailrpaiao,.

В о писа н ном устpoHicTiae IrfoMHiMo сдвигoIB воз можно также вы полне н ие операции тран спонирования матрицы двоичных символов.

Предмет изобретения

Вычи слительно-логиче|ское устрой ство, соде ржащее магнитный .оперативный нако пи,тель информации с разрядными шинами, у силители вос произведевия, подключенные через соотвепствующие диоды IK регистру регенерация, матрицу ма пнипных сердечников ic прямоугодыной петлей ги стерезиса, про шитых взаимно перпендикулярными адресными и раз ряд ными шинами, а также первыми и

BToipbIIMH диапональными .шинами,, два peiaep;сивных дешифратора, регистр сдвигателя, отличаюи ееся тем, что, ic целью у прощения y!CITройст ва и повышения eiro бы стродейспвия, разрядные,ши ны матрицы подключены одними ко нцами ы;соопвет ствующим .разрядным ши нам о перативно го накопителя, а,другими конца ми — !K соот ветст1вующим входам у силителей воспроизведения, адресные шины мат р ицы под соеди,неданы к в,ыходам регистра сдвигателя, входы которого через IcooraeTIcTствую1щие диоды соеди нен ы с,выхода ми у силителей во сцроизведения, à!Irepaые и вторые диагоналыные шины матрицы подключены

cooTiBeTicTIBeIHIHo IK выходам перьвого и второго ре версивных,де шифраторов.

337824

Составитель В. Рудаков

Техред Л. Богданова

Редактор Е. Гончар

Корректор Е. Зимина

Типография, пр. Сапунова, 2

Заказ 2013/10 Изд. № 853 Тираж 448 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4/5