Разряд регистра сдвига

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 342223

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союэ Советских

Социалистических

Республин

Зависимое от авт. свидетельства М

Заявлено 04.Ч.1970 (№ 1434823/26-9) с присоединением заявки №

Приоритет

Опубликовано 14.V1.1972. Бюллетень № 19

Дата опубликования описания Зл 11.1972

М. 1хл. 6 11с 19, 00

Комитет по делам иэобретений и открытий ори Совете 1йинистрое

СССР

УДК 621.374.3(088.8) Автор изобретения

Г. И. Берлипков

Заявитель

РАЗРЯД РЕГИСТРА СДВИГА

Изобретение IoTIHIQIcHTIcя к а втоматийе и,вычислителыной тех нике, Из ве стен регHIcTp сдвига Hp МОП-TpaIHçè сторах, содержащий два каскада с трех фазиы,м у пра вле нием.

Цель изобретен ия — расширс ние функцио нальных возможностей устройства.,Достигаепся о на тем, что пе р вый каскад предлагае.мого разряда выпол нен в виде сдвоенной д вух вхо дной схемы «И — ИЕ», выход которой ,непос редст веосно с|вязàIí со входом, второго

KBIcKBäà, причем затворы двух IIIocJIBHOIBBтелыно соединенных траизигторов одотой схемы «И — 1-?Е» подклю чеиы к шине узк|их инверсных сигналов сд вига и выходу второго каскада, а затворы двух госледовательно соеди ненных TpaHBHIcTopoiB другой схемы

«И — НЕ» соеди нены с шиной и м пульсо в сдвига и входом регистра через проходной

МОП-тра нзпстор, зат вор кото рого по дключен к щи не широких HIHIBcpсных cIHI HBJIoв импульсов сдвига.

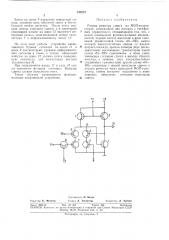

На чертеже представлена принцппиа льиая элект риче ская схе ма устройства.

Устройство, выполненное f а МОП-Tpа нзи,сторах 1 — 8, содержит гсва каскада с трехфаз н:ы,м уп,ра влен,ием. Первый каскад на

TpBIIIçHcTI0ðàx 3, 4, 6, 7 выпол не н в виде сд воен ной 3IByxIBxog,овой схемы «И — IE», В Ы Х 0 Д К От О Р О Й Н Е П О СР Е Д СгПВ Е Н Н О С В Я 3 а H 1С О входо м второго каскада на трагнзисторе 5.

Затворы транзисторов 8 и 4 подключе ны соответст ве н но к шине 9 узких HHIBUpc Hblx сигIHBJIoIB сд вига .и выходу второго каскада иа транзисто ре 5, а затворы тра нзистор ов 6 и 7 соединены c шиной 10 импульсов сдвил;а и входом 11 регистра через проходной МОПтра нзистор 8, затвор которого подключен к шине 12 пиироких инвср сных сигналов пм10 пульсов сдвига.

Исто|сник 13 служит для пита ни я схесмы, а и сточник 14 — для смещения нагрузочных транзисторов 1, 2 илп выработки сигналов моиоимпульсного питаигля узлов 15 и 16 схе15 мы.

В определенный момент инве рсные сигналы на Illинах 9 и 12 уменьшаются до уровня логического «нуля», отключая затвор траизи20 стора 7 от,информационного входа 11 и разрывая цепь обратной связи внутри ячейки.

В cëåäóþùHé момечгт на вход транзистора

6 поступает импульс сдвига, благодаря которому шгформация, задс ржаппая па затворе

25 транзистора 7, переписывается на выход схемы (узел 16), Синхронизируя с этим моментом импульсное питание затворов транзисторов 1, ?, можно использовать монопмпульсное питание для уменьшения мощности, потрсо30 ля "m ой регистром сдв1сга.

342223

Предмет изобретения

1ч 13

Составитель Л. Багян

Техред Л, Богданова

Корректор Л. Орлова

Редактор Б. Федотов

Заказ 2009!12 Изд. № 835 Тираж 405 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-З5, Раушская паб., д. 4/5

Типография, пр, Сапунова, 2

Затем на шине 9 нара стает и н версный сигнал, замыкая цепь обратной связи в бистабильной ячейке регистра. После этого с падаеп сипнал,импульса сдвига, и в некоторый сле дуюаций момент на шине 12 нарастает инверсный сигнал, подклю чающий затвор транзистора 7 к информа цио нному входу 11.

На этом цикл работы уcTIpoHIcTIB2 зака нчивает ся. Уровни сипналоз на входе 11 и шине 9 соответствуют уровням информационных ситна JQIB в схе ме, и только ин версный ,и м пульс на ши не 12 должеп1 иметь повышенную амплитуду для коммутации вентиля (тр анзистор а 8) .

При подключении входа 11 .к узлу 15 схе. ма выпол няст функции счетчи ка. Импульс сдвига служит и,м пульсом счета.

Таким образом рас шпря ютс я фун кциоIHàльные возмож ност и устройства.

Разряд репистра сдвига на МОП-пранзи,сторах, содержащий,два каскада с трехфазным упра влспием, отличающийся тем, чло, с целью расширения фтн1кционгльных возмож. ностей, первый каскад выполнении в виде сд военной д вух вхо

1-IЕ» соединены с шиной импульсо|в сдвига и входом регистра ч ерез про|ходной МОП-транзистор,:затвор которого подключен к ши не ши|роких инверсных сипнало в и мпульсо в

20 сдв и га.