Преобразователь последовательного кода грея в параллельный двоичный код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советснин

Социалистичеснив

Республин

Зависимое от авт. свидетельства №

М. Кл. 6 06f 5/04

Заявлено 19.Х.1970 (№ 1488493/18-24) с нрнсосдttttct»tcttt заявки ¹

Приоритет

Опубликовано 07.VII.1972. Бюллетень № 21

Дата опубликования описания 25Л П.1972

Ксвтитет па делам изобретений и атнрытий ори Сосете Министров

СССР

УД 1<, 681.325.53 (088.8) В. Я. Смирнов и Ю. Г. Шершуков

Авторы изобретения

Заявитель

ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА

ГРГЯ В ПАРАЛЛЕЛЬНЫ 1! ДВОИЧНЫЙ КОД

Изобретение относится к области автоматики и вычислительной техники и предназначено для преобразования кодов.

Известны преобразователи кода Грея в двоичный код, содержащие триггерные регистры. При использовании распределителя в таких устройствах может быть осуществлено преобразование последовательного кода Г рея в параллельный двоичный код.

Предложенное устройство отличается тем, что вход распределителя соединен с шиной подачи кода Грея, выходы разрядов распределителя — с входами соответствующих схем

«ИЛИ» согласно порядку следования разрядов кода Грея; выход каждой схемы

«ИЛИ» связан с входом схемы «ИЛИ» предыдущего младшего разряда, а выход старшего разряда распределителя — с единичным входом триггера старшего разряда трнггерпого регистра.

Это обеспечивает упрощение устройства и его быстродействие при произвольном порядке следования разрядов кода Грея.

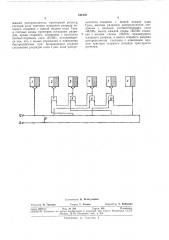

На чертеже показана схема устройства при следующем порядке следования разрядов кода Грея: Аь Вь Ав Вв, Аа, Вз (где А,, А2, Аа, B„ B2, Ва — первый, второй, третий, четвертый, пятый, шестой разряды соответственно) .

Устройство содержит триггерный регистр на триггерах 1 — б, схемы «ИЛИ» 7 — 10, распрсдслитсль 11, шину 12 пода ш кода Грея ti шину 18 TBI

Устройство работает следующим образом.

Импульсы кода Грея подаются на вход триггера 1 н вход распределителя ll. Импульс Bt с выхода распределителя 11 посгуиаст на вход триггеров 4, 8, 2 через схемы

«ИЛИ» 9, 8, 7.

Следующий импульс <1 проходит на вход

10 триггера 2 черсз схему «ИЛИ» 7, а импульс

В чсрсз схемы «ИЛИ» 10, 9, 8, 7 — на вход триггеров 5, 4, 8, 2.

Импульс Аа подается на вход триггеров 8, 2 через схемы «ИЛИ» 8, 7, а последний рас15 прсделснный импульс Ва на вход триггера б и одновременно через схемы «ИЛИ» 10, 9, 8, 7 на входы триггеров 5, 4, 8, 2. В результате триггер 1 суммирует по 2 все разряды кода

Грея, триггер 2 — все разряды кода Грея, 20 кроме первого, триггер 8 — все разряды кода

Грея, кроме первого и второго и т. д. В итоге, в триггерах 1 — б оказывается записанным двоичный код, соответствующий коду Грея, причем в триггере 1 записывается млад25 ший разряд двоичного кода, в триггере

2 — второй разряд двоичного кода и т. д.

Предмет изобретения

Преобразователь последовательного ;<ода

30 Грея в параллельный двоичный код, содер344438

Составитель В. Игнатущенко

Техред T. Ускова

Корректор T. Бабакина

Редактор И. Грузова

Заказ 2297/11 Изд. № 996 Тираж 406 Подписное

Е1НИИПИ Комитета по делам изобретений и открытий при Совете Мипистрон СССР

Москва, )К-35, Раугпская иаб., д. 4/5

Типография, пр. Сапунова, 2 жащий распределитель, триггерный регистр, счетный вход триггера младшего разряда которого соединен с шиной подачи кода Грея, а счетные входы триггеров остальных разрядов, кроме старшего, соединены с выходами соответствующих схем «ИЛИ», отличающийся тем, что, с целью упрощения и повышения быстродействия при произвольном порядке следования разрядов кода Грея, вход распределителя соединен . с шиной подачи кода

Грея, выходы разрядов распределителя соединены с входами соответствующих схем

«ИЛИ», выход каждой схемы «ИЛИ» соединен с входом схемы «ИЛИ» предыдущего младшего разряда, а выход старшего разряда распределителя соединен с единичным входом григгера старшего разряда три ггерного регистра.