Патент ссср 344507

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Свита Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 06.Х1.1970 (№ 1489706/18-24) с присоединением заявки №

Приоритет

Опубликовано 07.VI).1972. Бюллетень ¹ 21

Дата опубликования описания 27Л 11,1972

М. Кл. G Ilc 19/00

Комитет по делам иэобретений и открытий прн Совете Министров

СССР

УДК 686.326.33(088.8) Автор изобретения

Г. И. Берлинков

Заявитель

ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА

Изобретение относится к области автоматики и вычислительной техники.

Известны схемы двухкаскадных динамических регистров сдвига на МДП-транзисторах с индуцированным каналом, содержащие две шины импульсного питания, подключенные к затворам нагрузочных транзисторов каскадов.

Предлагаемый динамический регистр сдвига состоит из четырех МДП-транзисторов и отличается от известных тем, что затвор нагрузочного транзистора каждого каскада соединен с истоком переключательного транзистора другого каскада, а исток нагрузочного транзистора первого каскада — с затвором переключательного транзистора второго каскада, сток которого является выходом схемы.

Это позволяет упростить схему регистра.

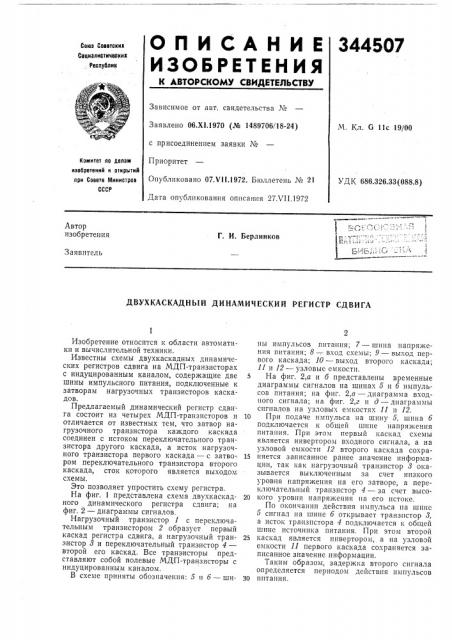

На фиг. 1 представлена схема двухкаскадного динамического регистра сдвига; нa фиг. 2 — диаграммы сигналов.

Нагрузочный транзистор 1 с переключательным транзистором 2 образует первый каскад регистра сдвига, а нагрузочный транзистор 8 и переключательный транзистор 4— второй его каскад. Все транзисторы представляют собой полевые МДП-транзисторы с индуцированным каналом.

В схеме приняты обозначения: 5 и б — шины импульсов питания; 7 — шина напряжения питания; 8 —. вход схемы; 9 — выход первого каскада; 10 — выход второго каскада;

l1 и 12 — узловые емкости.

5 На фиг. 2,а и б представлены временные диаграммы сигналов на шинах 5 и б импульсов питания; на фиг. 2,в — диаграмма входного сигнала; на фиг. 2,г и д — диаграммы сигналов на узловыx емкостях П и 12.

10 При подаче импульса на шину 5, шина б подключается к общей шине напряжения питапия. При этом первый каскад схемы является инвертором входного сигнала, а на узловой емкости 12 второго каскада сохра15 няется записанное ранее значение информации, так как нагрузочный транзистор 8 оказывается выключенным за счет низкого уровня напряжения на его затворе, а переключательный транзистор 4 — за счет высо20 кого уровня напряжения на его истоке.

По окончании действия импульса на шине

5 сигнал на шине б открывает транзистор 8, а исток транзистора 4 подключается к общей шине источника питания. При этом второй

25 каскад является инвертором, а на узловой емкости 11 первого каскада сохраняется записанное значение информации, Таким образом, задержка второго сигнала определяется периодом действия импульсов

Зо питания.

344507

l !

I ! ФЬг..2

Составитель С. Яворовская

Техред Т. Ускова

Редактор И; Грузова

Корректор, Е. Зимина

Заказ. 2253/10 Идд; М 975 Ти,р,аж 496, Подписное

ЦНИИПИ Комитета по делам изобретений и, открытий ври. Совете. Мщщстров. СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, нр. Сапунова, 2

Надежное функционирование схемы может быть обеспечено в том случае, всели епад импульса на шине б опережает во времени нарастание импульса на шине 5, а спад импульса на шине 5 опережает нарастание импульса на шине б. Кроме того, уровень логического «0», до которого нарастает напряжение на узловой емкости при действии высокого потенциала на истоке переключающего транзистора, не должен превышать порогового напряжения элементов схемы.

Предмет изобретения

Двухкаскадный динамический регистр сдвига на транзисторах со структурой ме4 талл — диэлектрик — полупроводник (МДПтранзисторах), содержащий две шины импульсного питания, подключенные к затворам нагрузочных транзисторов каскадов, отличающийся тем, что, с целью упрощения регистра, затвор нагрузочного транзистора каждого каскада соединен с истоком перекл1очательного транзистора другого каскада, а исток нагрузочного транзистора первого

1о каскада соединен с затвором переключательного транзистора второго каскада, сток которого соединен с выходной клеммой регистра.