Л. б. родини к. б. турецкийj: ;i ^i>&

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 344585

ИЗОБРЕТЕНИЯ

М АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союэ Советскик

Социалистическик республик

Зависимое от авт. свидетельства ¹

Заявлено 04 1.1971 (№ 1622449/26-9) с присоединением заявки ¹

Приоритет

Опубликовано 07.V11.1972. Бюллетень ¹ 21

Дата опубликования описания 20.VII.1972

М. Кл. Н 03k 19/08

Комитет по делам иэобретений и открытий при Совете Министров

СССР

УДК 621.374.3 (088.8) Авторы изобретения

Л. М. Бодина, В. Ф. Кравцунова, Г. А. Подольский, Л. Б. одйн и К. Б. Турецкий

Заявитель

ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Предлагаемая быстродействующая схема логического элемента может быть использована при проектировании дискретных или интегральных схем вычислительных устройств.

Известные логические элементы, содержащие входной многоэмиттерный транзистор, промежуточный транзистор и выходной каскад, состоящий из последовательно включенных инвертирующего и нагрузочного транзисторов, имеют низкое быстродействие, а также содержат технологически неосвоенные элементы.

В предлагаемом элементе коллектор и база промежуточного и инвертирующего транзисторов соединены соответственно с эмиттером и коллектором рассасывающих транзисторов, а базы рассасывающих транзисторов через резистор подключены к базе многоэмиттерного тр анзистора.

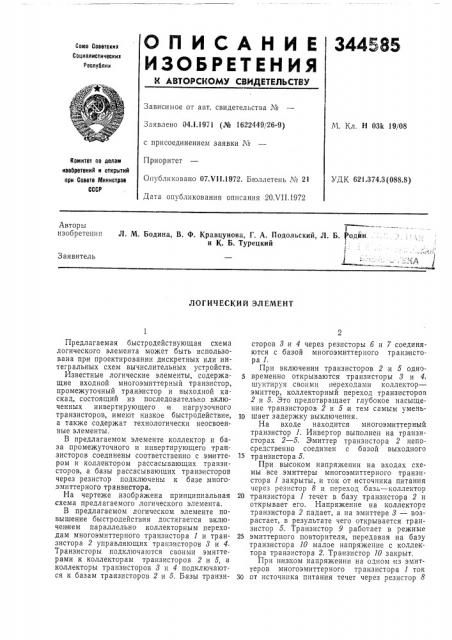

На чертеже изображена принципиальная схема предлагаемого логического элемента.

В предлагаемом логическом элементе повышение быстродействия достигается включением параллельно коллекторным переходам многоэмиттерного транзистора 1 и транзистора 2 управляющих транзисторов 3 и 4

Транзисторы подключаются своими эмиттерами к коллекторам транзисторов 2 и 5, а коллекторы транзисторов 8 и 4 подключаются к базам транзисторов 2 и 5. Базы транзисторов 3 и 4 через резисторы б и 7 соединяются с базой многоэмиттерного транзистора l.

При включении транзисторов 2 и 5 одно5 временно открываются транзисторы 8 и 4. шунтируя своими переходами коллектор— эмиттер, коллекторный переход транзисторов

2 и 5. Это предотвращает глубокое насыщение транзисторов 2 и 5 и тем самым умень10 шает задержку выключения.

На входе находится многоэмиттерный транзистор l. Инвертор выполнен на транзисторах 2 — 5. Эмиттер транзистора 2 непосредственно соединен с базой выходного

15 транзистора 5.

При высоком напряжении на входах схемы все эмиттеры многоэмиттерного транзистора 1 закрыты, и ток от источника питания через резистор 8 и переход база — коллектор

20 транзистора 1 течет в базу транзистора 2 и открывает его. Напряжение на коллекторе транзистора 2 падает, а на эмиттере 8 — возрастает, в результате чего открывается транзистор 5. Транзистор 9 работает в режиме

25 эмиттерного повторителя, передавая на базу транзистора 10 малое напряжение с коллектора транзистора 2, Транзистор 10 закрыт.

При низком напряжении на одном пз эмиттеров многоэмиттерного транзистора 1 ток

30 от источника питания течет через резистор 8

344585

Предмет изобретения

Составитель Ю. Еркин

Техред Т. Курилко

Редактор Е. Гончар

Корректор 3. Тарасова

Заказ 2196/16 Изд. № 946 Тираи 406 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 и этот эмиттер. Транзистор 1 открывается и на базе транзистора 2 появляется низкий потенциал. Транзистор 2 и вслед за ним транзистор 5 закрываются. Транзисторы 8 и 4 также закрываются.

Во время переходного процесса при включении транзисторы 8 и 4 закрыты, что ведет к быстрому открыванию транзисторов 2 и 5 и, следовательно, малой величине задержки включения. Затем открываются транзисторы

8 и 4 и уменьшают степень насыщения транзисторов 2 и 5.

Во время переходного процесса при выключении транзисторы 8 и 4 закрываются в инверсном режиме и подготавливают быстрое выключение транзисторов 2 и 5 в активном режиме.

Рассасывание коллекторного заряда транзистора 5 и перезаряд емкости нагрузки 11 осуществляется также за счет открывания транзисторов 9 и 10.

Логический элемент, содержащий входной многоэмиттерный транзистор, промежуточ.ный транзистор и выходной каскад, состоящий из последовательно включенных инвер10 тирующего и нагрузочного транзисторов, отличающийся тем, что, с целью повышения быстродействия при сохранениями совместимости с интегральной технологией, в нем коллектор и база промежуточного и инвертиру15 ющего транзисторов соединены, соответственно, с эмиттером и коллектором рассасывающих транзисторов, а базы рассасывающих транзисторов через резистор подключены к базе многоэмиттерного транзистора.