Устройство для изменения масштаба времени накапливаел1ой информации

Иллюстрации

Показать всеРеферат

О П И САН И Е

ИЗОБРЕТЕНИЯ

3455I9

Соаз Соввтскик

Сациалистичвскил

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 03.Х1 1970 (№ 1489656/18-24) с присоединением заявки №

Приоритет

Опубликовано 14. т1111972. Бюллетень ¹ 22

Дата опубликования описания 4.VIII.1972.Ч. Ь,л. G 1lc 21/00

Комитат по долам ивобрвтвниЯ и открытиЯ при Соввтв Министров

СССР

УДК 681.327(088.8) Авторы изобретения М. М. Сухомлинов, В. М. Никитенко, Б. В. Саинчина и В. Г. Масол

Заявитель

Институт автоматики

УСТРОЙСТВО ДЛЯ ИЗМЕНЕНИЯ МАСШТАБА ВРЕМЕНИ

НАКАПЛИВАЕМОЙ ИНФОРМАЦИИ

Изобретение относится к техническим средствам для научных исследований. Оно может быть использовано в составе вычислительного комплекса или самостоятельно, для изменения масштаба времени (частоты сигнала) накапливаемой информации с целью уменьшения непроизводительных потерь машинного времени, в частности при спектральном и корреляционном анализах, а также для уплотпения каналов связи, регистрации,и запоминания аналоговых и дискретных сигналов, Известны устройства для временного сжатия входного сигнала. Однако в таком уcTройстве одному блоку памяти соответствует один коэффициент сжатия, что ограничивает диапазон исследуемых частот, увеличивает время отработки, и влияет на точность анализа. Последнее объясняется тем, что реализация входного сигнала постепенно обновляется в процессе анализа с некоторым смещением.

Целью изобретения является создание устройства для изменения масштаба времени накапливаемой информации (транспониатора 2), обладающего расширенными техническими параметрами по сравнению с параметрами прототипа (коэффициенты сжатия — 64, 1024, 2048 и соответственно диапазоны изменения частот входного сигнала — 0 — 4 кгц, 0 — 240 eII, 0 — 120 гт1, частотой выдачи выходных сигналов — 500 кгт1) и расширенными функциональными возможностями за счет использования трех ячеек памяти.

Эта цель достигается использованием в за5 поминающем устройстве трех ячеек памяти на магнитострикционных линиях задержки, оригинальной схемы управления и применением комму TGTopa настройки, с помощью которого производятся переключения логических

10 элементов схемы управления и соединение блоков памяти в различных комбинациях.

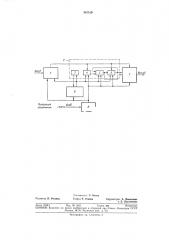

На чертеже представлена блок-схема устройства.

Она содержит преобразователь аналог—

15 код 1, запоминающий блок 2, в который входят управляющие магнитострикционные линии задержки 8 МЛЗ, и три ячейки памяти

4 — 6, выходной преобразователь код — аналог

7, блок управления 8 запоминающим блоком

20 и коммутатор настройки 9.

Выход преобразователя 1 соединен с информационными входамп ячеек памяти 4, 6 и со входом преобразователя 7. Выходы ячейки памяти 4 соединены со входами ячейки памя25 ти 5, а выходы ячеек памяти 5 и 6 соединены со входами друг друга и входами преобразователя код †анал 7. Вход блока 8 соединен с выходом МЛЗ 8, а выход блока 8— со входами преобразователя МЛЗ 8, а также

30 с управляющими входакш ячеек памяти 4 — 6.

345519

Выход коммутатора настройки 9 соединен с питающими входами логических схем преобразователя 1, блока 8 ячеек 4 — б и преобразователя 7.

Устройство может работать в следующих режимах:

РЕЖИМ № 1. Коэффициснт сжатия — 64, диапазон часгот исследуемых сигналов—

0 — 4 кгпв, время хранения пачки 262 яксек.

Используются три ячейки памяти 4 — 6, В качестве буферного накопителя применена ячейка памяти 4. Две других ячейки памяти включены между собой последовательно и непрерывно обновляют информацию пачка«ш по 64 слова после заполнения накопителя.

РЕЖИМ № 2. Коэффициент сжатия — 64, диапазон частот исследуемого сигнала

0 — 4 кгпв, время хранения реализации из 1024 точек 131 яксгк. Используются три ячейки памяти, две из которых (4 и 5) — буферные накопители.

РЕЖИМ Мо 3. Коэффициент сжатия — 1024, диапазон частот исследуемых сигналов—

0 — 240 га, время хранения значения одного измерения 2,1 сек. Используется ячейка памяти б с непрерывным обновлением информации (без буферного накопителя) .

РЕЖИМ ¹ 4. Коэффициент сжатия — 2048, диапазон частот исследуемых сигналов—

0 — 120 ги, время «ранения значения одного измерения 8,4 сек. Используются две ячейки памяти 5 и б, которые включены последовательно и имеют оощую цепь циркуляции.

В запоминающем блоке происходит непрерывное обновление информации (без буферного накопителя).

Контрольные режимы предназначены для проверки правильности работы блоков транспониатор а 2.

Два режима служат для проверки работы преобразователя аналог — код и выходного преобразователя код †анал. При этом с помощью коммутатора настройки из активных элементов блока управления запоминающим блоком образуются необходимые функциональные узлы для автономной работы преобразователя аналог — код.

Два других режима предназначены для проверки и наладки запоминающего блока.

Необходимые специфические функциональные узлы при этом образуются из активных элементов преобразователя аналог — код и блока управления запоминающим блоком.

Транспониатор 2 может работать в режиме с буферным накопителем или без него.

При работе устройства с буферным накопителем коммутатором настройки устанавливается соответствующий режим (например,¹1).

Входной сигнал, характеризующий случайный процесс, подается на вход преобразователя 1. Последний запускается от блока 8 и преобразует аналоговый входной сигнал в

40 цифровую форму. Через цикл раооты управляющих МЛЗ 8 блок 8 считывает информацию с преобразователя 1 и снова запускает его для следующего цикла преобразователя.

Преобразованный входной сигнал в виде шестиразрядного параллельного кода поступает в буферный накопитель (4), на шесть магнитострикционпы«линий задержки. После заполнения ячейки памяти 4 производится перекладка информации в ячейки памяти 5 и б, которые соединены между собой последовательно. После этого цикл заполнения ячейки памяти 4 и перекладка информации в ячейки памяти 5 и б повторяются. Соотношение емкостей всех ячеек памяти выбрано так, что заполнение ячейки памяти 5 и ячейки памяти б производится последовательно, слово за словом. После их заполнения происходит обновление информации, причем стирание старой информации производится словами.

Из ячейки памяти б информация параллельным шестпразрядным кодом подается на преобразователь 7, который восстанавливает первоначальную форму в одного аналогового сигнала, но с частотой в К раз большей (К вЂ” коэффициент сжатия) .

Время хранения дискретной информации в блоке 2 определяется временем заполнения ячейки памяти 4 и временем цикла обновления информации в ячейках памяти 5 и б.

Прп работе устройства без буферного накопителя используется одна ячейка памяти, входы которой подключены к выходу преобразователя 1, а выходы — к преобразователю 7.

Информация параллельным кодом, слово за словом, заполняет блок 2 и после его заполнения продолжает обновляться. При этом одновременно с вы«ода блока 2 информация поступает па преобразователь 7.

Предмет изобретения

Устройство для изменения масштаба времени накапливаемой информации, содержащее преобразователь аналог — код и запоминающий блок, управляющие входы которых соединены с блоком управления на магнитострикционных линиях задержки, преобразователь код — аналог и коммутатор настройки, отличающееся тем, что, с целью расширения функциональны«возможностей и улучшения технических характеристик, запоминающий блок содержит три ячейки памяти, причем выходы преобразователя аналог — код через коммутатор настройки соединены со входами первой и третьей ячеек памяти и преобразователя код — аналог, выходы первой ячейки памяти соединены со входамп второй, а выходы второй и третьей ячеек памяти соединены соответственно со входами третьей и второй и входом преобразователя код †анал.

345519

Редактор Л. Утехина

Заказ 3310/7 Изд. № 1033 Тираж 406 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4. 5

Типография, пр. Сапунова, 2

Составитель С. Белан

Техред T. Ускова

Корректоры: А. Николаева и E. Ласточкина