Устройство селекции импульсов в приемнике для многоканальной асинхронной аппаратурысвязи

Иллюстрации

Показать всеРеферат

О П И- С А-=И-И Е 345625

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства М

М. Кл. Н 04j 1/12

Заявлено 12.XI.1970 (№ 1494059126-9) с присоединением заявки №

Приоритет—

Опубликовано 14.И1.1972. Бюллетень № 22

Дата опубликования описания ЗХ111.1972

Комитет по делам изобретений и открьций при Совете министров

СССР

УДК 621.374.33(088,8) Автор изобретения

О. Г. Каратаев

Заявитель

УСТРОЙСТВО СЕЛЕКЦИИ ИМПУЛЬСОВ В ПРИЕМНИКЕ

ДЛЯ МНОГОКАНАЛЬНОЙ ACHHXPOHHOlf АППАРАТУРЫ

СВЯЗИ

Изобретение относится к радиотехнике.

Известно устройство селекции импульсов в приемнике для многоканальной асинхронной аппаратуры связи, содержащее две линии задержки с отводами, амплитудный и фазовый детекторы, перемножитель, интегратор, потенциальную схему совпадения, две дифференцирующие цепочки, пороговую схему и схему совпадения.

Это устройство малоэффективно, поскольку импульсы адреса, подаваемые на вход селектора, изменяются в процессе распространения, кроме того, возможно наложение импульсов нескольких каналов.

Целью изобретения является улучшение селекции импульсов адреса, искаженных импульсами других каналов.

Поставленная цель достигается тем, что фазовый детектор через первую дифференцирующую цепочку подключен ко входу первой линии задержки, отводы которой через перемножитель подключены к первому входу интегратора. Ко второму входу интегратора подключена схема совпадения, ко входу которой через соответствующие отводы второй линии задержки подключен амплитудный детектор. Выход схемы совпадения через вторую дифференцирующую цепочку подключен к первому входу потенциальной схемы совпадения, второй вход которой подключен к выходу интегратора, а выход потенциальной схемы совпадения подклточен к пороговой схеме.

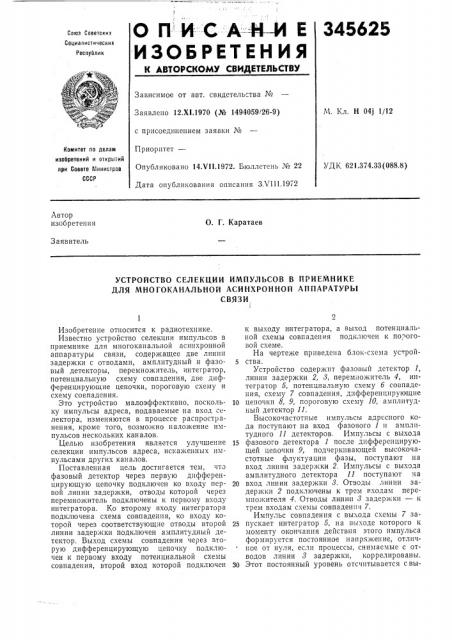

На чертеже приведена блок-схема устрой5 ства.

Устройство содержит фазовый детектор 1, линии задержки 2, 8, перемножитель 4, интегратор 5, потенциальную схему б совпадения, схему 7 совпадения, дифференцирующие

1о цепочки 8, 9, пороговую схему 10, амплитудный детектор 11.

Высокочастотные импульсы адрссного кода поступают на вход фазового 1 и амплитудного 11 детекторов. Импульсы с выхода

15 фазового детектора 1 после днфферснцирующей цепочки 9, подчеркивающей высокочастотные флуктуации фазы, поступают на вход линии задержки 2. Импульсы с выхода амплитудного детектора 11 поступают на

20 вход линии задержки 8. Отводы линии задержки 2 подключены к трем входам перемножителя 4. Отводы линии 3 задержки — к трем входам схемы совпаденн» 7.

Импульс совпадения с выхода схемы 7 за25 пускает интегратор 5, на выходе которого к моменту окончания действия этого импульса формируется постоянное напряжение, отличное от нуля, если процессы, снимаемые с отводов линии 8 задержки, коррелированы.

ЗО Этот постоянный уровень отсчитывается с вы345625

Составитель А. Горбачев

Техред Т. Ускова Корректор Т. Бабакина

Редактор Т. Орловская

Заказ 330?/13 Изд. № 1019 Тираж 406 Подписное

ЦНИИПИ Комитета по делам изобретений н открытий прн Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 хода потенциальной схемы б совпадения с помощью подаваемого на ее второй вход с дифференцирующей цепочки 8 импульса, совпадающего с задним фронтом импульса совпадения.

Импульс в выхода схемы б совпадения фиксируется с помощью пороговой схемы 10.

Предмет изобретения

Устройство селекции импульсов в приемнике для многоканальной асинхронной аппаратуры связи, содержащее две линии задержки с отводами, амплитудный и фазовый детекторы, перемножитель, интегратор, потенциальную схему совпадения, две дифференцирующие цепочки, пороговую схему и схему совпадения, отличающееся тем, что, с целью улучшения селекции импульсов адреса, искаженных импульсами других каналов, фазовый детектор через первую дифференцирующую цепочку подключен ко входу первой линии задержки, отводы которой через перемножитель подключены к первому входу интегратора, а ко второму входу последнего подключена схема совпадения, ко входу которой через соответствующие отводы второй

10 линии задержки подключен амплитудный детектор, при этом выход схемы совпадения через вторую дифференцирующую цепочку подключен к первому входу потенциальной схемы совпадения, второй вход которой подlS ключен к выходу интегратора, а выход потенциальной схемы совпадения подключен к короговой схеме.