Распределитель импульсов

Иллюстрации

Показать всеРеферат

3479I2

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сома Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

М. Кл. Н 031< 13/258

Заявлено 27.1Ч.1970 (№ 1433,300. 26-9) с присоединением заявки ¹

Приоритет

Опубликовано 10.Ч!11.1972. Бюллетень № 24

Дата опубликования описания 4.IX.1972

Комитет по делам изобретений и открытий ори Совете Мииистров

СССР

УДК 621,374.3,3 (088.8) Авторы изобретения

В. М. Брук и Л. 3. Гильченок

Заявитель

РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к системам отсчета передачи и приема дискретной информации.

Известен распределитель импульсов, содержащий двухтактный регистр с и двоичными ячейками, ко входу которого подключено устройство формирования последовательности тактовых импульсов; две группы подключенных к регистру дешифраторов, каждая из которых состоит из к рядов по и схем совпадения в ряду, где 1(z(n, и блок управления, имеющий к, триггеров.

Предлагаемое изобретение сокращает число элементов и повышает надежность устройства.

Описываемое устройство достигается тем, что выход и-ой схемы совпадения к-го ряда второй группы дешифраторов подключен к четному входу к-го и нечетному входу к + 1-го триггеров блока управления, а нечетный выход к триггера блока управления подключен ко входам всех схем совпадения к-ых рядов первой и второй групп дешифраторов.

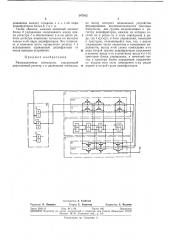

На чертеже приведена блок-схема предлагаемого р асп редел ителя и м пуль сов.

Данный распределитель состоит из регистра 1 на двоичный элементах 2, 8, 4, 5, блока б дешифраторов первой группы, блока 7 дешифраторов второй группы, выполненных на схемах совпадения, и блока 8 управления, представляющего собой совокупность и двоичных элементов, Каждый цикл работы регистра 1 делится на два полуцикла. В первом полуцикле происходит поочередное переключение двоичных элементов 2 —:5 регистра в состояние «единица», во втором — поочередная установка двоичных элементов регистра, начиная с первого, в состояние «ноль».

Сигналы на выходе блока б дешифраторов первой группы появляются в первом полуцик10 ле работы регистра 1, на выходе блока 7 дешифраторов второй группы — во втором полуцикле.

Каждый к-ый дешифратор из блока 6, где

1(к(>г, составляет пару с к-ым дешифрато15 ром нз блока 7.

Любая к-ая пара дешнфраторов связана с выходом к-го двоичного элемента блока 8 управления, а последний выход к-го дешифратора блока 7 связан с единичным входом к-го и

20 с нулевым входом в к+ 1-ом двоичном элементе блока 8 управления.

Благодаря этому после выдачи сигналов с к-ой пары дешифраторов блоков б, 7 во втором цикле регистра 1 последний сигнал к-ro

25 дешифратора блока 7 дешифраторов второй группы переключает к-й двоичный элемент блока 8 управления в исходное состояние (при этом запрещается выдача сигналов с к-ой пары дешифраторов) и к+ 1-ый двоичный эле30 мент блока 8 управления — в состояние, раз347912

Предмет изобретения

Составитель А. Горбачев

Редактор Л. Лаврова Техред E. Борисова Корректор Е. Исакова

Заказ 2645 13 Изд. М 1120 Тираж 406 Подписное

ЦНИИПИ Комитета по делам изооретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 решающее выдачу сигналов с к+ 1-ой пары дешифраторов блока б, 7 и т. д.

Таким образом, каждый двоичный элемент блока 8 управления «запоминает» номер цикла регистра 1 и обеспечивает в к-ом цикле работы регистра появление сигналов на выходах только к-ой пары дешифраторов. Это позволяет в конечном итоге «укоротить» регистр 1 и использовать одинаковые дешифраторы от числа выходов устройства.

Распределитель импульсов, содержащий двухтактный регистр с п двоичными ячейками, ко входу которого подключено устройство формирования последовательности тактовых импульсов, две группы подключенных к регистру дешифраторов, каждая из которых состоит из к рядов по и схем совпадения в ряду, где 1(к(а, и блок управления, имеющий к триггеров, отличающийся тем, что, с целью сокращения числа элементов и повышения надежности, выход и-ой схемы совпадения к-го

10 ряда второй группы дешифраторов подключен к четному входу к-ro и нечетному входу к+1-го триггеров блока управления, а нечетный выход к триггера блока управления подключен ко входам всех схем совпадения к-ых рядов

15 первой и второй групп дешифраторов.