Частотно-импульсный интегратор

Иллюстрации

Показать всеРеферат

3500I3

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВМДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 21.1.1971 (№ 1618911/18-24) с присоединением заявки №

Приоритет

Опубликовано 04.1Х.1972. Бюллетень ¹ 26

Дата опубликования описания 9.XI.1972

М, Кл, 6 06g 7/18

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 681.142.07(088.8) Авторы изобретения

Г. О. Паламарюк, М. Б. Никифоров и В. С. Новичков

Рязанский радиотехнический институт

Заявитель

ЧАСТОТНО-ИМПУЛЬСНЫЙ ИНТЕГРАТОР

Изобретение относится к области вычислительной техники и может быть использовано при построении частотно-импульсных вычислительных устройств, интерполяторов, частотно-импульсных дифференциальных анализаторов и др.

Известный частотно-импульсный интегратор, выполняющий операцию интегрирования по невременному параметру, содержит блок для получения первой производной, частотноимпульсный множительно-делительный блок, блок коммутации, реверсивный счетчик и триггер знака.

Однако известное устройство обладает весьма низкой точностью, так как строб, управляющий работой .вентиля, формируется с помощью стандартизатора импульсов, длительность, которых нестабильна.

Цель изобретения — повышение точности воспроизведения операции интегрирования, обеспечение возможности интегрирования во всех четырех квадрантах и сохранение формы представления входной информации в выходном сигнале.

Это достигается включением частотно-импульсного множительно-делительного устройства, состоящего всего из двух триггеров, трех импульсно-потенциальных схем совпадения и дешифратора на четыре входа и обладающего высокой точностью, которая зависит только от стабильности опорной частоты на входе, деления (при использовании кварцевого генератора стабильность опорной частоты может быть порядка 10 — ), подключением блока коммутации знаковых шин реверсивного счетчика, управляющего режимом работы реверсивного счетчика в зависимости от сочетания знаков входных частот, знака производной и знака интеграла, и подключением к выходам

10 триггеров реверсивного счетчика двоичного умножителя частоты.

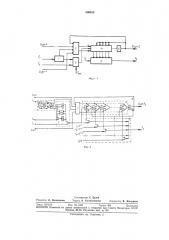

На фпг. 1 н 2 даны схемы предлагаемого частотно-импульсного интегратора.

Предлагаемый интегратор состоит из блока

15 1 для получения первой производной сигнала аргумента Г,(t), часотно-импульсного множительно-делительного блока 2, блока коммутации 8, реверсивного счетчика 4, двоичного умножителя 5 и триггера знака б.

20 Шина входной часоты аргумента F>(t) соединена со входом блока I для получения первой производной, импульсный выход которого соединен с одним из входов умножения множительно-делительного блока ), а потен25 циальный знаковый выход соединен со входом блока коммутацин 8 знаковых шин реверсивного счетчика 4. Ко второму входу умножения частотно-импульсного множитсльно-делительного блока 2 подключена шина входной

30 частоты подпнтегральной функции Г,(t), а ко

350013 ! входу деления — шина опорной стабильной частоты F„. Выход множительно-делительного блока соединен со входом реверсивного счетчика 4, импульсный выход которого сое динен со входом триггера зиака б, выход ко- 5 торого является выходной шиной знака и, кроме того, соединен с установочными входами нуля всех триггеров реверсивного счетчика, кроме последнего, и со в)ходом блока ком. мутации 3 знаковых шин. К двум другим вхо- 10 дам блока 8 подключены входные шины знака сигналов F, и F, Выходы блока 3 соединены со знаковыми шинами реверсивного счетчика 4. Выход двоичного умножителя б является выходом устройетва. 15

Предлагаемое устройство работает следующим образом.

На выходе дифференцирующего блока получаем первую производную аргумента F.,(i) равную 20

dFx (Э(1

4

Ф+ — Sign,у Sign x Sign . Signz(/

1 х/ Sign у-: Sign х :Sign Sign z /

dt

\/ Sign y Sign х Ядп — Sign z V

dx.

dt >,/ Ядп у Sign x. Sign †„ Sign z \у >/ Sign у . Sign x. Sign Sign z Q

dt

Q Sign y.Sign x Sign —..Sign zg .

dx

Н

Q Sign y Sign x.Sign — Signzg Sign y p

Х Sign x Sign Sign z. (Х

dt

P =P а с помощью блока умножения произведение

K>Fy (/) dFx (/)/dx . j

Fon получаем

Преобразовав код в частоту, йолучим:

" F, = N: = I F,,(t)dF„(0"=

0Л

;0

СЛ

=К,IF (>)Ю„(/), 0

Для обеспечения работы интегратора во всех четырех квадрантах введен блок знака, коммутирующий входные шины двоичного реверсивного счетчика в зависимости от сочетания зйаков входных и выходных сигналов.

l 1

Блок коммутации знаковых шин реверсивного счетчика 8 представляет собой простой дешифратор, имеющий четыре входа и два выхода. Функции возбуждения выходов дешифратора Р+ и P имеют вйд: которое интегрируется по временному параметру, образуя выходной сигнал в виде кода:

Предмет изобретения

1. Частотно-импульсный интегратор, содержащий блок для получения первой производной, частотно-импульсный множительно-делительный блок, блок коммутации, реверсивный

50 счетчик и триггер знака, отличающийся тем, что, с целью повь|шения точности и упрощения устройства, импульсный выход блока для получения первой производной соединен со входом умножения частотно-импульсного мно35 жительно-делительного блока, второй вход умножения которого соединен с источником подынтегральной функции, вход деления соединен с источником опорной частоты, а выход соединен со входом реверсивного счетчика, 40 выход реверсивного счетчика подключен ко входу знакового триггера, выход которого подключен к установочному входу нуля триггеров реверсивного счетчика и к одному из входов блока коммутации, к трем другйм вхо 45 дам которого подключены знаковый выход блока для получения первой производной и входные знаковые шины аргумента и подынтегральной функции, а выходы соединены со знаковыми шинами реверсивного счетчика.

50 2. Устройство по п. 1, отличающееся тем, что, с целью сохранения) формы представления входной информации, оно содержит двоичный умножитель, потенциальные входы которого соединены с выходами триггеров ре

55 версивного счетчика, а импульсный вход — с источником опорной частоты.

350013 с

Фиг 7

)! Оп

Фиг 2

Составитель С. Белан

Техред А. Камышникова

Редактор Л. Василькова

Корректор В. Жолудева

Типография, пр. Сапунова, 2

Заказ 3974/13 Изд. № 1459 Тираж 406 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, SK-35, Раушская наб., д. 4/5