Устройство для проверки функционирования логических схем

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 354415

ИЗОБРЕТЕНИЯ

Сома Советских

Социалистически, Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт, свидетельства №вЂ”

Заявлено 19.V.1970 (№ 143027i0/18-24) М. Кл. G 06f 11100 с присоединением заявки ¹â€”

Приоритет

Опубликовано 09.Х.1972. Бюллетень № 30

Дата опубликования описания 10.XI.1972

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 621.396.6.013.,3-50 (088.8) Авторы изобретения

Ю. А. Зубаков и С. А. Зверьков

Заявитель

УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ФУНКЦИОНИРОВАНИЯ

ЛОГИЧЕСКИХ СХЕМ

Изобретение относится к вычислительной технике, в частности к устройствам тестового ,контроля логических схем: типовых элементов замены ЭВМ, схем цифровых приборов, больших интегральных схем и т. д.

Известны устройства для тестового контроля, содержащие блок входных сигналов, блок эталонйых выходных сигналов, схему сравнения, блок ввода данных, блок коммутации, схему индикации неисправностей, блок управления.

Цель изобретения — улучшение качества контроля на максимальной рабочей частоте.

Это достигается тем, что в устройство дополнительно введены блок контролируемых выходов, выполненный в виде магазинного запоминающего устройства переменного объема, и блоки контрольных регистров. Выход блока контролируемых выходов подключен к второму входу схемы сравнения, один вход в к выходу блока ввода, другой — к выходу блока управления. Вход одного блока контрольных регистров подсоединен к выходу блока входных и эталонных выходных сигналов, а вход другого — к выходу блока контролируемых выходов. Одни выходы блоков контрольных регистров подключены к соответствующим входам блока индикации, другие — к входам блока управления, управляющие входы — к выходам блока управления, а входы сравнения — к соответствующим выходам блока ввода. Предлагаемое устройство позволяет проводить контроль работоспособности логической схемы при проверке элементов схемы на переключение из состояния «О» в состояние «1» и наоборот.

Для осуществления проверки схемы на переключение вводят оператор переключения.

10 Если при изменении входных сигналов на входах элемента элемент изменяет сигнал на выходе с «1» на «О», выходу приписывается прямое переключение, а при обратном изменении сигналов — обратное переключение.

15 |Тест для неисправности рассматривают как последовательность тестовых наборов, при подаче которой переключение сигналов, по крайней мере, одного контролируемого выхода исправной схемы отличается от переключе20 ния сигналов контролируемого выхода схемы с неисправностью.

При построении теста используют формализованный метод построения тестов, основанный на нахождении чувствительного пути.

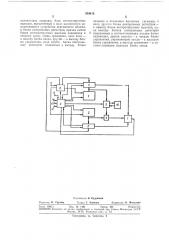

25 На чертеже показана блок-схема устройства для проверки функционирования логических схем.

Устройство содержит блок 1 входных и эталонных выходных сигналов; блок 2 контроли30 руемых выходов; коммутатор 3; блок 4 срав 354415 пения; блоки 5 и 6 контрольных регистров; блок 7 индикации; блок 8 ввода данных; блок

9 управления. ,Блок 1 входных и эталонных выходных сигналов, реализованный на магазинной памяти 5 переменного объема, обеспечивает хранение и выдачу последовательности входных и эталонных выходных сигналов теста.

Блок 2 контролируемых выходов, реализованный на магазинной памяти переменного 10 объема, хранит и выдает последовательность контролируемых выходов на каждом временном такте работы проверяемого устройства.

Коммутатор 8 подсоединяет: входы проверяемого устройства к триггерам выходного ре- 15 гистра магазинной памяти блока 1, которые содержат сигналы входных полюсов проверяемого устройства; эталонные выходные сигналы с выходного регистра магазинной памяти блока 1 на блок сравнения; выходы проверяе- 20 мого устройства на блок 4 сравнения. Блок 4 сравнивает сигналы контролируемых выходов проверяемого устройства и эталонных выходных сигналов на каждом временном такте работы проверяемого устройства. 25

Блоки 5 и б контрольных регистров со схемами сравнения на нуль обеспечивают поразрядный контроль работы магазинных памятей по модулю два после подачи последовательности входных и эталонных выходных сигна- 30 лов теста и последовательности контролируемых выходов.

Блок 7 индикации неисправности проверяемого устройства фиксирует неисправность в случае несравнения эталонных выходны сиг- 35 налов и сигналов контролируемых выходов проверяемого устройства, фиксируемого блоком сравнения, и равенства нулю контролируемых регистров после подачи теста.

Блок 8 ввода осуществляет последователь- 40 ный ввод данных в блок коммутации — данных о внешних входах проверяемого устройства, в контрольные регистры — дополнения по модулю два, последовательности входных и эталонных выходных сигналов теста в блок 45 входных и эталонных выходных сигналов, последовательности контролируемых выходов в блок контролируемых выходов.

Блок 9 управления обеспечивает; начальную установку устройства; осуществление ре- 50 жимов проверки, однократного, циклического; управление объемом и сдвигом магазинных памятей блоков 1 и 2; управление вводом данных; анализ состояния схем, сравнения контрольных регистров на нуль; управление работой блока индикации неисправности.

Проверяемая логическая схема 10 должна иметь не более и внешних логических полюсов, где n — число разрядов выходных регистров магазинных памятей блоков 1 и 2. 60

Для проверки схемы последовательность входных и эталонных выходов сигналов теста для неисправности схемы не должна превыШать Шмакс (m„„„.ñ — МаКСИ МаЛЬНОЕ ЧИСЛО РЕ гистров магазинной памяти блока 1). 65

Перед началом работы устройства на вход

11 блока ввода данных поступает входная информация в двоичном позиционном коде по и входным каналам, Блок 8 ввода данных последовательно передает информацию о внешних входах проверяемой логической схемы на блок 8, на блок 1 — последовательность входных и эталонных выходных сигналов теста, на блок 2 — последовательность контролируемых выходов, на контрольные регистры поступают соответствующие дополнения по модулю два, На входе 12 задается объем магазинных запоминающих устройств, на входе 18 — рабочая частота проведения испытаний, на входе 14 устанавливается один из возможных режимов испытания: однократный или циклический.

При проведении однократных испытаний на входы проверяемой схемы дается тестовая последовательность с частотой проведения испытаний, блок 4 определяет реакцию контроли руемых выходов на,каждом такте работы устройства. В случае несравнения сигналов хотя бы на одном контролируемом выходе результат несравнения передается на блок 7 индикации.

При подаче всего теста для неисправности проверяется состояние схемы сравнения контрольных регистров на нуль, в блоках 5, б при равенстве нулю на блок 7 выдается разрешение на индикацию неисправности. При неравенстве нулю контрольных регистров в блок 9 управления выдается сигнал о неисправности в работе магазинных запоминающих устройств блоков l и 2.

Во время проведения циклических испытаний проводится неоднократная подача тестовой последовательности, которая обеспечивается циклическим сдвигом тестовой информации в магазинных памятях переменного объема. В циклическом режиме проверка контрольных регистров в блоках 5 и б на нуль осуществляется на каждом нечетном цикле проверки на данном тесте.

После проверки схемы на одном тесте подается следующий тест и процесс повторяется до тех пор, пока схема не будет проверена на всех тестах, в этом случае на блок управления поступает сигнал останова по входу 15.

Предмет изобретения

Устройство для проверки функционирования логических схем, содержащее блок ввода данных, соединенный с входом блока входных и эталонных выходных сигналов, выполненного в виде магазинного запоминающего устройства„выход которого подключен через коммутатор сигналов к контролируемой логической схеме и через блок сравнения к блоку индикации, блок управления, подключенный своими выходами к блоку ввода данных, блоку входных и эталонных выходных сигналов, коммутатору и к блоку индикации, отличающееся тем, что, с целью улучшения качества контроля на максимальной рабочей частоте, оно до354415

Составитель В. Кудрявцев

Техред Т. Курилко

Корректор В, Жолудева

Редактор И. Грузова

Заказ 3686 1 Изд. № 1486 Тираж 406 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж 35, Раушская наб., д. 4/5

Типография, пр, Сапунова, 2 полнительно содержи г блок контролируемых выходов, выполненный в виде магазинного запоминающего устройства переменного объема, и блоки контрольных регистров, причем выход блока контролируемых выходов подключен к второму входу схемы сравнения, один вход— к выходу блока ввода, другой — к выходу блока управления, вход одного блока контрольных регистров подключен к выходу блока входных и эталонных выходных сигналов, а вход другого блока контрольных регистров— к выходу блока контролируемых выходов, одни выходы блоков контрольных регистров подключены к соответствующим входам блока индикации, другие выходы —.к входам блока управления, управляющие входы — к выходам блока управления, а выходы сравнения — к соответствующим выходам блока ввода.