Овое сглаживающее устройств

Иллюстрации

Показать всеРеферат

356644

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Совка Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

М. Кл. б 06f 7/38

Заявлено 27.VII.1970 (№ 1471763!18-24) с присоединением заявки ¹

Приоритет

Опубликовано 23.Х.1972. Бюллетень № 32

Дата опубликования описания 12.ХП.1972

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 681.3:519.2 (088.8) Авторы изобретения

Э. А. Саакян, Г. Я, Бахчиев и П. И. Погребецкий

Заявитель Тбилисский филиал Всесоюзного научно-исследовательского института метрологии им. Д. И. Менделеева

Ь 1

ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВ

Изобретение относится к области измерительной техники и может быть использовано в аппаратуре анализа статистических характеристик случайных процессов.

Предлагаемое цифровое сглаживающее устройство предназначается для производства операций сглаживания знакопеременных случайных процессов.

Известное цифровое сглаживающее устройство с передаточной функцией К(р) =

1 предназначенное для осуществле1+рР ния сглаживания знакопеременного процесса, отличается большим объемом оборудования (два множительных устройства, реверсивный счетчик, распределитель и сравнивающее устройство), сложной коммутацией узлов и низким быстродействием.

Целью изобретения является существенное упрощение схемы и повышение быстродействия цифрового сглаживающего устройства.

Поставленная цель достигается тем, что входной сигнал подается в виде двоичного числа на входы п младших разрядов (п+т) разрядного сумматора, выходы старших и разрядов которого связаны с соответствующими входами п разрядного регистра, п выходами поразрядно подключенного через логический элемент «ИЛИ» к входам п младших разрядов сумматора, старший разряд которо2 го через логический элемент «ИЛИ» и триггера знака соединен с младшим разрядом сумматора.

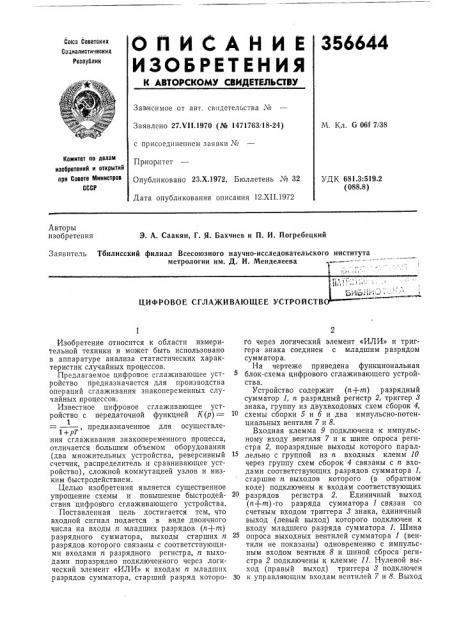

На чертеже приведена функциональная блок-схема цифрового сглаживающего устройства.

Устройство содержит (и+т) р азрядный сумматор 1, и разрядный регистр 2, триггер 8 знака, группу из двухвходовых схем сборок 4, схемы сборки 5 и 6 и два импульсно-потенциальных вентиля 7 и 8.

Входная клемма 9 подключена к импульсному входу вентиля 7 и к шине опроса регистра 2, поразрядные выходы которого параллельно с группой из и входных клемм 10 через группу схем сборок 4 связаны с п входами соответствующих разрядов сумматора 1, старшие и выходов которого (в обратном коде) подключены к входам соответствующих разрядов регистра 2. Единичный выход (п+т)-го разряда сумматора 1 связан со счетным входом триггера 8 знака, единичный выход (левый выход) которого подключен к входу младшего разряда сумматора 1. Шина

25 опроса выходных вентилей сумматора 1 (вентили не показаны) одновременно с импульсным входом вентиля 8 и шиной сброса регистра 2 подключены к клемме 11, Нулевой выход (правый выход) триггера 8 подключен

ЗО к управляющим входам вентилей 7 и 8. Выход

356644

55 вентиля 7 параллельно с клеммой 12 связан с входами старших m разрядов сумматора 1 через схему сборки 5 и со счетным входом триггера 8 через схему сборки б. Клемма 18 подключена к шине перезаписи обратного кода из старших п разрядов сумматора 1 в регистр 2. Группа из (п+т) выходных клемм 14 связана с выходами (в прямом коде) соответствующих разрядов сумматора.

Старшие п выходных клемм 14 соответствуют выходным клеммам целой части выходного числа, а т младших клемм — дробной части.

В исходном состоянии в регистре 2 сумматора 1 и в триггере 8 зафиксирован код нуля.

Вентили 7 и 8 закрыты.

В описываемом устройстве реализуется цифровой алгоритм оператора экспоненциального сглаживания (оператора Брауна)

1 а;= а; y+ — (х; — ag >), К где х; — текущее -ое значение исходного процесса; а; — -ое значение сглаженного процесса.

К = 2 " = 7 др, где Т вЂ” интервал сглаживания; р — частота преобразования входного сигнала.

Вышеприведенный оператор сглаживания имеет передаточную функцию

1+т

Устройство работает следующим образом.

Пусть в сумматоре 1 после (i — 1)-го шага работы устройства зафиксирован двоичный код числа а; ь а в регистре 2 — двоичный код целой части числа а, ь но противоположного знака, а в триггере 8 — знак числа а; i. Если а; <)0, то триггер 8 находится в положении нуля, вентили 7 и 8 закрыты. Если а, <<0, то триггер 8 находится в положении единицы, вентили 7 и 8 открыты.

Определение а; осуществляется за четыре такта.

В такте t> на клемму 9 подается импульс, который производит перепись двоичного кода числа (— а; 1) из регистра 2 через группу схем сборок 4 в младшие п разрядов сумматора 1. После завершения суммирования в старших и разрядах сумматора 1 фиксируется

"С вЂ” 1 код целой части числа а, — а в младших п разрядах — дробная часть указанной разности. В такте 12 через группу из п клемм 10 и группу схем сборок 4 в младшие и разрядов сумматора 1 заносится двоичный

15 го г5

ЗО

40 код числа х; (в прямом коде, если х;)0, или в обратном коде, если x;<0), а через входную клемму 12 — знак х; (если х,<0, то на входы старших т разрядов сумматора 1 через схему сборки 5 и на счетный вход триггера 8 через схему сборки б заносится кодовая единица).

В старших п разрядах сумматора 1 фиксируется код целой части числа а ° 1 Х;

l7- — — — + — t г/е гщ а в и младших разрядах — код дробной части.

В такте t3 на клемму 11 подается импульс, который производит опрос сумматора 1 и вентиля 8. На группе из (n+m) выходных клемм

14 появляется код числа а;, а на выходной клемме 15 — знак числа а;. Если а;)О, то выдается прямой код числа cr,, на клемме 15 импульс не появляется, если же а;<0, то число а; выдается в обратном коде, а на клемме 15 появляется импульс, указывающий на отрицательность числа а;. Одновременно с этим в такте t3 производится сброс регистра 2.

В такте t4 на входную клемму 18 подается импульс, производящий перезапись обратного кода целой части числа а; (старших п разрядов числа n,) из сумматора в регистр 2.

Таким образом, i-ый шаг работы устройства завершается; (i+1) -ый шаг работы осуществляется в последовательности, описанной на -ом шаге.

В целях повышения точности вычислений необходимо разрядности регистра 2 и сумматора 1 увеличивать в сторону младших разрядов. При этом необходимо выход схемы сборки 5 подать и на входы младших дополнительных разрядов сумматора, а единичный выход триггера 8 подключить к входу младшего разряда сумматора 1.

Предмет изобретения

Цифровое сглаживающее устройство, содержащее сумматор, регистр, триггер знака, логические элементы «И» и «ИЛИ», отличаюи ееся тем, что, с целью упрощения схемы и повышения быстродействия, выходы старших и разрядов сумматора связаны с соответствующими входами п разрядного регистра, выходами поразрядно подключенного через логический элемент «ИЛИ» к входам п младших разрядов сумматора, старший разряд которого через логический элемент «ИЛИ» и триггера знака соединен с младшим разрядом сумматора.

356644

И 9

Редактор Е. Семанова

Заказ 3948/19 Изд. № 1574 Тираж 406 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Составитель В. Орлова

Техред Л. Богданова

f2 о

Корректоры: Л. Корогод и М. Коробова