Сесоюзная iрйтег?гно-т?агы':г-н/ш^!

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 359645

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сова Советских

Содиалистическик

Республик

Зависимое от авт. свидетельства _#_

Заявлено 01 11.1971 (№ 1623222/18-24) с присоединением заявки №

Приоритет

Опубликовано 21.XI.1972. Бюллетень ¹ 35

Дата опубликования описания 27.XI I.1972

М. Кл. G 06f 3/04

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 681.327.11(088.8) Авторы изобретения

Г. В. Никулин и В. Л. Тиме

Заявитель

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ВЫВОДА СИГНАЛОВ

УПРАВЛ EH ИЯ ИЗ ВЫЧИСЛИТЕЛЬНОЙ МАШИ Н Ы

Изобретение относится к области вычислительной техники и может быть использовано, например, в устройствах ввода — вывода управляющих вычислительных машин.

Известны многоканальные устройства для вывода сигналов управления из вычислительной машины, содержащие блок управления, подключенный к элементам памяти. Основным недостатком таких устройств является возможность выр аботки ложных сигналов управления в результате отказов, возникающих при работе устройства, что может привести к нарушению всего процесса управления.

Цель изобретения — повышение достоверности вывода информации. Это достигается тем, что предлагаемое устройство содержит одноразрядный двоичный счетчик, блок свертки по модулю два и блок распознавания ошибки. Одноразрядный двоичный счетчик соединен с управляющим входом блока управления и с одним из входов блока свертки по модулю два, другие входы которого соединены с выходами элементов памяти, а выходы его подключены к блоку распознавания ошибки.

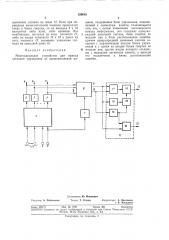

На чертеже дана блок-схема описываемого устройства.

Устройство содержит кодовые шины l адреса, входящую шину 2 информации, управляющий вход 8 блока 4 управления, элементы 5 памяти, выходные шины б кодовой информации, одноразрядный двоичный счетчик 7, блок

8 свертки по модулю два с прямым 9 и инверсным 10 выходами и блок 11 распознавания ошибки с выходными шинами 12 и 18, схемами «НЕ» 14 и 15, схемами «И» lб — 18 и схемой «ИЛИ» 19, Устройство работает следующим образом.

При обращении вычислительной машины к устройству на входные кодовые шины 1 и 2

10 и управляющий вход 8 поступают соответствующие сигналы. Блок 4 управления вырабатывает сигнал записи принятой информации в один из элементов 5 памяти в соответствии с кодом адреса на шинах 1. При этсм

15 состояние соответствующей выходной ксдогой шины б изменяется на противоположное. Кроме того, сигнал обращения к устрокству поступает нг вход счетчика 7, изменяя его состояние. Если отказов в работе устройства

20 нет, то на прямом выходе 9 блока 8 находится нуль, а на инверсном выходе 10 — единица. Эта комбинация сигналов, поступая на вход блока П распознавания ошибки, не изменяет состояния его выходов, а на выход25 ных шинах 12 и 18 сигналов нет. Если х е при обращении вычислительной машины происходит отказ собственно устройства, то на выходе 9 блока 8 присутствует единица, а на выходе 10 — нуль. Эта комбинация, посту30 пая на элементы 14 и lб блока 11, вызывает

359645

Предмет изобретения

Составитель Ю. Мовшович

Корректоры: А. Васильева и В. )Колудева

Редактор А. Пейсоченко

Техред Т. Ускова

Заказ 4227/1 Изд. № 1762 Тираж 406 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 5К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 появление сигнала на шине 12. Если при обращении вычислительной машины происходит отказ в блоке свертки, то на выходах 9 и 10 находятся либо нули, либо единицы. Эти комбинации, поступая на вход элемента 17, либо на входы элементов 15 и 18 и далее на вход элемента 19, вызывают появление сигнала на выходной шине 18.

Многоканальное устройство для вывода сигналов управления из вычислительной машины, содержащее блок управления, подключенный к элементам памяти, отличающееся тем, что, с целью повышения достоверности вывода информации, оно содержит однораз5 рядный двоичный счетчик, блок свертки по модулю два и блок распознавания ошибки, причем одноразрядный двоичный счетчик соединен с управляющим входом блока управления и с одним из входов блока свертки по

10 модулю два, другие входы которого соединены с выходами элементов памяти, а выходы его подключены к блоку распознавания ошибки.